# Switching-Speed Limitations of Ferroelectric Negative-Capacitance FETs

Zhi Cheng Yuan, Shahriar Rizwan, Michael Wong, Kyle Holland, Sam Anderson, Terence B. Hook, Diego Kienle, Serag Gadelrab, *Senior Member, IEEE*, Prasad S. Gudem, *Senior Member, IEEE*, and Mani Vaidyanathan, *Member, IEEE*

Abstract—Recently, negative-capacitance FETs (NCFETs) have been proposed to reduce subthreshold slope and help continue supply-voltage scaling alongside channel-length scaling. We investigate the high-frequency switching behavior of NCFETs using the Landau–Khalatnikov equation to model ferroelectric materials. Multidomain interactions in the ferroelectric are considered, resulting in strong agreement with experimental measurements. Operation of NCFETs at gigahertz frequencies is investigated with this experimentally validated multidomain model. We find that the effectiveness of the voltage amplification in NCFETs is strongly dependent on the viscosity coefficient  $\rho$  of the ferroelectric, and that a low  $\rho$  (<0.1  $\Omega$ ·m) is required for the operation at the high gigahertz frequencies.

Index Terms—Ferroelectric, Moore's law, negative capacitance, negative-capacitance FETs (NCFETs), subthreshold slope.

#### I. Introduction

S MOORE'S law continues and transistors scale to eversmaller dimensions, the electronics industry is becoming increasingly concerned with managing the power density in large digital chips [1], [2]. One way to reduce this power density is to use transistors with a steep slope, i.e., a low subthreshold swing (SS). However, conventional transistors are fundamentally limited to  $SS \ge 60$  mV/decade by Boltzmann mechanics. Recently, the exploitation of ferroelectric materials has gained much attention as a potential way to break this 60 mV/decade limit [3]–[6].

In ferroelectric materials, the crystal lattice is stable at a state that exhibits a spontaneous polarization, which can be flipped by applying an electric field to deform the crystal to the opposite state [7], [8]. A capacitor made with such a

Manuscript received June 5, 2016; revised August 12, 2016; accepted August 16, 2016. Date of publication September 7, 2016; date of current version September 20, 2016. This work was supported in part by the Natural Sciences and Engineering Research Council of Canada, in part by Alberta Innovates-Technology Futures, and in part by Alberta Innovation & Advanced Education. The review of this paper was arranged by Editor B. Kaczer.

- Z. C. Yuan, S. Rizwan, M. Wong, K. Holland, S. Anderson, and M. Vaidyanathan are with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB T6G 2R3, Canada (e-mail: maniv@ualberta.ca).

- T. B. Hook is with IBM Corporation, Essex Junction, VT 05452 USA.

- D. Kienle is with the Theoretische Physik I, Universität Bayreuth, 95440 Bayreuth, Germany.

- S. Gadelrab is with Qualcomm Canada Inc., Markham, ON L3T 7W3, Canada.

- P. S. Gudem is with Qualcomm Inc., San Diego, CA 92121 USA.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2016.2602209

ferroelectric material can exhibit "negative capacitance," where the stored charge in a stable state is negative with respect to the applied voltage. Such negative capacitance can be exploited for "voltage amplification," by making the voltage across a second capacitor placed in series with a ferroelectric larger than that applied to the series combination. This voltage amplification can be exploited in the gate-stack of a transistor in order to achieve SS < 60 mV/decade [3].

Although negative-capacitance phenomena have been studied in various forms [9]–[15], the idea to use ferroelectrics to create "negative-capacitance FETs" (NCFETs), in which voltage amplification from negative capacitance is utilized to realize SS < 60 mV/decade, came to prominence only very recently, as a result of the work of Salahuddin and Datta [3]. Subsequently, negative capacitance in lead zirconium titanate (PZT) was experimentally validated [16], and thereafter, NCFETs using ferroelectrics demonstrated experimentally [17]-[19], with SS values of 42 mV/decade [17] and 8.5 mV/decade [18]. However, all the experimental works done thus far on NCFETs have considered only static (dc) device behavior, rather than dynamic (transient switching) behavior. While a few studies have experimentally measured the transient response of isolated ferroelectric capacitors [16], [20], the dynamic response of NCFETs incorporating ferroelectrics thus remains relatively unexplored, especially for operation at frequencies relevant in present-day, high-speed digital electronics.

In this paper, we present a multidomain simulation methodology based on the Landau–Khalatnikov (LK) equation to probe the dynamic behavior of NCFETs. With the parameters of the ferroelectric material calibrated to the experimental data presented in [16], we simulate a digital inverter–inverter configuration and show that, given the ferroelectric materials currently known, NCFETs may lose their advantage over conventional FETs when operating at frequencies in the gigahertz range.

## II. METHODOLOGY

## A. Simulated Circuits

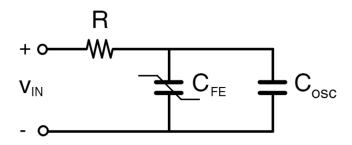

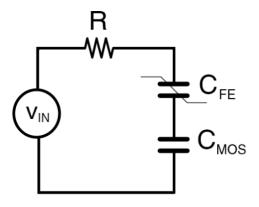

We perform two switching simulations in order to investigate the ferroelectric described in Section II-B. The first setup, shown in Fig. 1, emulates the experimental measurement in [16]. An input voltage source  $v_{\rm IN}$  stepping

0018-9383 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 1. First simulation setup, corresponding to the experimental measurement in [16].

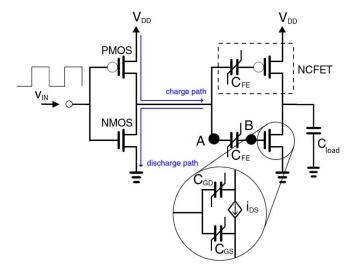

Fig. 2. Second simulation setup, corresponding to a high-speed digital inverter–inverter model.

between -5.4 and +5.4 V, with a period of 120  $\mu$ s, is placed in series with a 50 k $\Omega$  resistor and a ferroelectric (thickness  $t_{\rm FE}=60$  nm and area  $A=30~\mu{\rm m}\times30~\mu{\rm m}$ ). An oscilloscope, represented as a 60-pF capacitor  $C_{\rm OSC}$ , appears in parallel with the ferroelectric capacitor  $C_{\rm FE}$ .

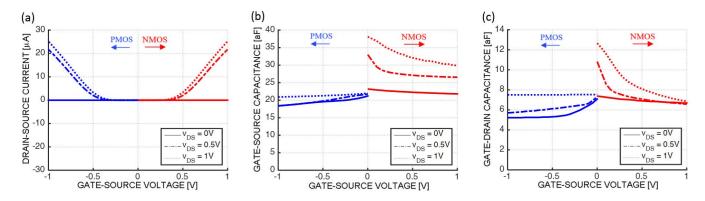

The second setup, shown in Fig. 2, is constructed to obtain an understanding of the impact of ferroelectrics in high-speed digital circuits. We model a digital inverter-inverter configuration at the 28-nm node, with each MOSFET enhanced by a ferroelectric capacitor in series with its gate, the combination thus yielding an NCFET, as shown in Fig. 2. Here, the ferroelectric capacitor has dimensions  $t_{\rm FE}=6$  nm and  $A = 90 \text{ nm}^2$ , with the thickness and area chosen for capacitance matching with the MOSFET in order to maximize voltage amplification [3], [21]. The conventional nMOS and pMOS transistors are modeled as voltage-dependent gate capacitances  $C_{GS}(v_{GS}, v_{DS})$  and  $C_{GD}(v_{GS}, v_{DS})$ , combined with a voltage-dependent current source  $i_{DS}(v_{GS}, v_{DS})$ , where  $v_{\rm GS}(t)$  and  $v_{\rm DS}(t)$  are the gate-source and drain-source voltages, respectively, both dependent on time t. The voltage dependencies, shown in Fig. 3, were determined using Cadence Spectre simulations [22]. Both nMOS devices have gate dimensions of 30 nm × 30 nm. The pMOS devices have double the channel width as the nMOS devices, with dimensions of 60 nm × 30 nm, in order to reach a similar ON current as the nMOS devices of approximately 20  $\mu$ A.

The supply voltage  $V_{\rm DD}$  is taken to be 1 V. We consider the transient behavior of this inverter pair at frequencies varying from 5 to 500 MHz. In the first half of the cycle, the input to the second stage charges to  $V_{\rm DD}$  through the pMOS of the first inverter, while in the second half of the cycle, it discharges to ground through the nMOS of the first inverter. In both cases, we use the voltage-dependent current and capacitance data obtained from Cadence Spectre [22], shown in Fig. 3, to determine the circuit response through numerical simulation.

#### B. Modeling the Ferroelectric

Our simulation methodology is based on the LK equation [23], [24] for a ferroelectric capacitor ( $C_{FE}$  in Figs. 1 and 2)

$$\rho \frac{dP(t)}{dt} + \frac{dG}{dP} = 0 \tag{1}$$

where P(t) is the polarization, G is Gibb's free energy, and  $\rho$  is the viscosity.

The viscosity  $\rho$  in (1) accounts for the resistance of the ferroelectric to deformation, which is the mechanism for polarization switching, and hence,  $\rho$  accounts for the finite time required for switching to occur. The expression for Gibb's free energy appearing in (1) is

$$G = \alpha P^{2}(t) + \beta P^{4}(t) + \gamma P^{6}(t) - E(t)P(t)$$

(2)

where  $\alpha$ ,  $\beta$ , and  $\gamma$  are material coefficients specific to a chosen ferroelectric [25], and where

$$E(t) = \frac{v_{\text{FE}}(t)}{t_{\text{FE}}} \tag{3}$$

is the electric field across the ferroelectric, with  $v_{FE}(t)$  being the voltage across it.

Equations (1)–(3) apply to a ferroelectric crystal with a uniform polarization; in order to capture the effect of multiple domains and the resulting nonuniform polarization, we discretize the ferroelectric into a square lattice and consider the area  $A_i$  centered around each lattice point i to have a uniform polarization  $P_i(t)$ . A linear interaction factor ties together all neighboring lattice points [26], [27]. We thus modify (1) and (2) to apply to a nonuniform polarization, finally obtaining

$$\rho \frac{dP_{i}(t)}{dt} = \frac{v_{\text{FE}}(t)}{t_{\text{FE}}} + k \left[ \sum_{j} (P_{j}(t) - P_{i}(t)) \right] - 2\alpha_{i} P_{i}(t) - 4\beta_{i} P_{i}^{3}(t) - 6\gamma_{i} P_{i}^{5}(t)$$

(4)

where k is the interaction factor that describes the strength of the coupling between the nearest neighbor lattice points, the sum over j is the sum over all neighbors of i, and we assume that the entire ferroelectric crystal experiences a uniform electric field specified by (3). Finally, the charge on the ferroelectric capacitor is given by

$$Q(t) = \sum_{i} \left[ \varepsilon_0 \frac{v_{\text{FE}}(t)}{t_{\text{FE}}} + P_i(t) \right] A_i.$$

(5)

Fig. 3. Cadence Spectre [22] simulation results for a 28-nm FET. (a)  $i_{DS}(v_{GS}, v_{DS})$  curves of nMOS and pMOS. (b)  $C_{GS}(v_{GS}, v_{DS})$  curves for nMOS and pMOS. (c)  $C_{GD}(v_{GS}, v_{DS})$  curves for nMOS (red online) and pMOS (blue online).

Under these assumptions, (4) and (5) specify the nonlinear, time-dependent, charge-voltage (Q–v<sub>FE</sub>) relation for each element C<sub>FE</sub>, and they can be used with the corresponding current dQ(t)/dt through each element, and Kirchoff's laws, to determine the transient responses of the circuits in Figs. 1 and 2. The time-domain integration is performed using Euler's method with adaptive time step.

## C. Device Parameters

For the ferroelectric, we consider  $PbZr_{1-x}Ti_xO_3$ , where x=0.8 for the overall crystal. However, in order to capture variations within the ferroelectric, we assume that the material exhibits a random spread, with x uniformly distributed between 0.6 and 1; the resulting coefficients  $\alpha_i$ ,  $\beta_i$ , and  $\gamma_i$  in (4) can then be obtained using the expressions found in [25].  $\rho$  is fitted at 2  $\Omega$ ·m to produce good agreement with the experimental result. The validity of our model and the underlying assumptions are verified by strong agreement with experiment, as shown in Section III-A.

## III. RESULTS AND DISCUSSION

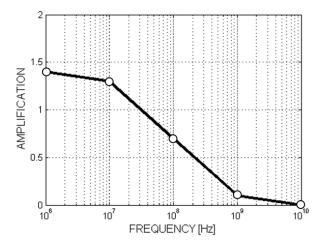

### A. Calibration with Experiment

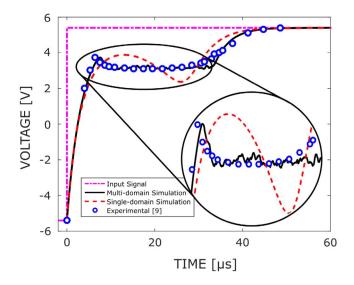

As shown in the exploded view of Fig. 4, our simulated transient response aligns very well with the experimental curves in [16], including the sharp peak followed by a rapid decay and subsequent rise.

Note that this signature behavior, and particularly the peaking, cannot be properly captured by a simulation that assumes uniform polarization, i.e., a single domain [16, Fig. 4(b)]. A multidomain model [specified by our (4) and (5)] is needed to account for nonuniform polarization. We found that, for the purposes of this calibration to experiment, a square lattice with 100 points in each direction was adequate for reproducing the experimental curves. As the voltage across the ferroelectric  $v_{\rm FE}$  climbs, it reaches the threshold required to cause the polarization at one lattice point of the ferroelectric crystal to flip, which, in turn, causes a cascading effect: the flipped polarization at one lattice point spreads to neighboring lattice points via the interaction factor k (modeling the shifting of domain walls), which results in

Fig. 4. Validation of our simulation methodology via a comparison with the experimental curves in [16]. Circles show experimentally measured values for the voltage  $v_{\rm FE}$  across the ferroelectric. Solid line shows the result of our multidomain simulation, which exhibits a strong match to experiment. Dashed lines show the result of a single-domain simulation. The input voltage is also shown as a dashed-dotted line.

a sharp drop in the electric field, and hence  $v_{\rm FE}$ . This drop then slows as the region of flipped domains spreads to cover a greater proportion of the crystal, and  $v_{\rm FE}$  resumes its steady climb, driven by the input signal, and the electric field thereby rises sufficiently to help flip the lattice points most resistant to a change in polarization. Clearly, capturing such behavior requires a nonuniform (multidomain) polarization approach.

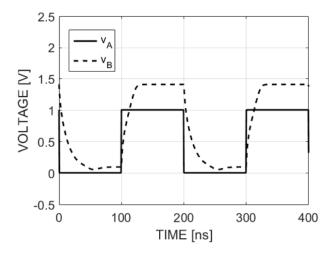

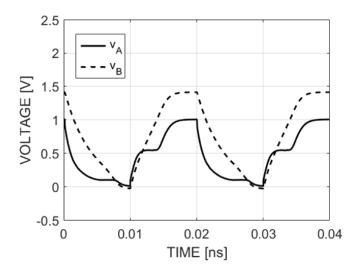

# B. Dynamic Behavior at Low Frequencies

Having calibrated our simulation to experiment, we now examine the switching behavior of an inverter (Fig. 2) in order to assess the viability of digital circuits using PZT NCFETs. We first consider operation at a frequency of 5 MHz. As shown in Fig. 5, our simulation confirms the voltage amplification effect of the ferroelectric at 5 MHz. The voltage at the internal node B (Fig. 2) (between the ferroelectric capacitor and the gate of the MOSFET) is 1.4 times greater

Fig. 5. Dynamic simulation of the circuit of Fig. 2 with an input signal at 5 MHz, showing verification of the voltage amplification effect.

Fig. 6. Dynamic simulation of the circuit of Fig. 2, with an input signal at 500 MHz, showing loss of voltage amplification, i.e., showing  $v_B < v_A$ , at a higher frequency (versus that for Fig. 5).

than that of node A (to the left of the ferroelectric capacitor), which demonstrates a voltage boosting effect created by the ferroelectric capacitor. This boost will allow for an effective SS lower than 60 mV/decade [3].

## C. Dynamic Behavior at High Frequencies

We then consider operation of this circuit at a frequency of 500 MHz. As shown in Fig. 6, at this frequency, the voltage amplification is lost, and the voltage at the internal node B in Fig. 2, i.e., between the ferroelectric capacitor and the gate of the MOSFET, is always lower than the voltage at node A to the left of the ferroelectric. We will now examine the reason for this result.

## D. Connection to P-E Hysteresis Curves

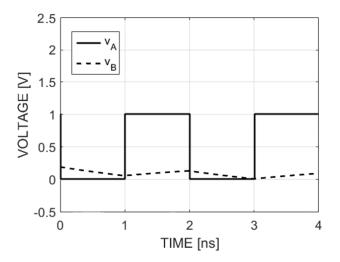

The reason for a lack of negative capacitance and hence voltage amplification at high frequencies (Fig. 6) can be understood by considering the P-E hysteresis curves of a

Fig. 7. Hysteresis curves at frequencies of (a) 10 MHz, (b) 100 MHz, (c) 1 GHz, and (d) 10 GHz, showing the symmetry breaking phenomenon at high frequencies.

ferroelectric. Since the ferroelectric crystal must physically distort in order to switch polarization states, there is a small but finite delay between a voltage input and the resulting response in polarization—a delay modeled through the viscosity  $\rho$  in our LK approach. It then follows that for an input at high frequencies, the polarization cannot keep pace, and therefore remains in a fixed state. This gives rise to a symmetry breaking effect at high frequencies [28], [29], as shown in the simulated P-E hysteresis curves in Fig. 7, where for illustration, we take E to be the electric field across a single-domain ferroelectric. For frequencies up to 1 GHz, the ferroelectric is able to reach both the positive and the negative polarization. However, as the frequency increases further, and certainly by 10 GHz, the electric field changes too quickly for the ferroelectric to respond, and the polarization remains trapped in one of the two stable states. Due to this trapped polarization state, the ferroelectric capacitor cannot exhibit negative capacitance, and hence voltage amplification cannot occur. These results are consistent with the experimental data for the switching kinetics of PZT; measured rise times are approximately 200 ps [20], suggesting an operating-frequency limit of about 2.5 GHz.

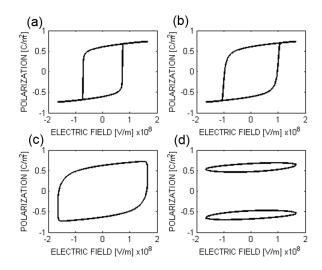

## E. Frequency Effects on Voltage Amplification

The impact of symmetry breaking at high frequencies is shown explicitly in Fig. 8. As shown, the voltage amplification, defined as the peak voltage at node B divided by the peak voltage at node A in Fig. 2, steadily decreases as the frequency increases and as symmetry breaking inhibits polarization switching and the negative-capacitance effect. It is worth adding that at very high frequencies, the insertion of the ferroelectric can actually lead to an attenuation of the voltage at B with respect to A. This phenomenon can be understood by considering the physical implications of the symmetry breaking of ferroelectric materials. At high frequencies, once symmetry breaking occurs [Fig. 7(d)], the ferroelectric is trapped in one of two polarization loops. In this case, the magnitude of the polarization change is small, i.e., the

Fig. 8. Dependence of voltage amplification in the circuit of Fig. 2 on frequency, as described in the text.

contribution of the term involving  $P_i(t)$  in (5) to the dynamic response is negligible at high frequencies; the ferroelectric behaves essentially as a linear capacitance  $\sim \epsilon_0 A/t_{\rm FE}$  that is small compared with the gate oxide capacitance  $\epsilon_{\rm ox}\epsilon_0 A/t_{\rm ox}$  of the MOSFET, where  $\epsilon_{\rm ox}$  is the relative permittivity of the oxide and  $t_{\rm ox}$  is its thickness, leading to the voltage *attenuation* visible in Fig. 8 at high frequencies.

## F. Generalization to Other Ferroelectric Materials

The previous analysis was performed on a specific composition of PZT and there is no obvious extension to other ferroelectric materials. However, with an RC circuit approximation of a switching NCFET, we show in the Appendix that the minimum possible time required to achieve voltage amplification within an NCFET configuration is

$$\tau_{\min} = \frac{\rho t_{\text{FE}}}{2} \left( \frac{C_{\text{MOS}}}{A} \right) \tag{6}$$

where  $C_{\text{MOS}}/A$  is the usual capacitance per unit area of the gate.

With this expression, we can determine a bound for  $\rho$  to obtain  $\tau_{\min} = 1$  ps, where 1 ps corresponds to the rise time of the inverter–inverter circuit in Fig. 2 in the absence of a ferroelectric material, i.e., the rise time with usual MOSFETs as opposed to NCFETs, and hence, the rise time representative of the modern and future processors working in the gigahertz to terahertz range.

A lower bound on the thickness for ferroelectrics is  $t_{\rm FE}=1$  nm, a value that can be found by accounting for the typical dimensions of a unit cell in ferroelectrics [30], and a reasonable minimum per-unit-area capacitance value for modern MOSFETs is  $C_{\rm MOS}/A{\sim}30$  fF/ $\mu$ m<sup>2</sup>, which can be deduced from the Cadence Spectre [22] simulation results shown in Fig. 3. With these values, to obtain  $\tau_{\rm min}=1$  ps, we find from (6) that  $\rho$  must be less than about 0.1  $\Omega \cdot$  m, independent of other material properties, a value considerably lower than the  $\rho=2$   $\Omega \cdot$  m value we used to match the experiments for PZT in Fig. 4. In fact, for PZT, using the same  $\alpha$ ,  $\beta$ , and  $\gamma$  material coefficients as we did for Fig. 4, we find  $\rho$

Fig. 9. Dynamic simulation showing voltage amplification in the circuit of Fig. 2 at 50 GHz for  $\rho=0.1~\text{m}\Omega\cdot\text{m}$ .

Fig. 10. Simplified NCFET switching circuit, with a voltage  $v_{\mbox{\footnotesize{IN}}}$  applied to the gate.

must be reduced to  $0.1~\text{m}\Omega\cdot\text{m}$  to achieve voltage amplification with a 1-ps rise time, as shown in Fig. 9. Note that the required  $\rho$  of  $0.1~\text{m}\Omega\cdot\text{m}$  is actually 1000 times lower than the value of  $0.1~\Omega\cdot\text{m}$  we found from (6), emphasizing that the latter value represents an *upper bound* on  $\rho$ , i.e., a *necessary* condition for any ferroelectric material to provide voltage amplification under high-speed operation.

## IV. CONCLUSION

The following conclusions can be drawn from this paper examining NCFETs operating under high-speed switching conditions.

- 1) Current studies on NCFETs focus on static measurements of subthreshold slope. We have identified an additional parameter  $\rho$  that strongly influences the high-frequency response of ferroelectric materials.

- 2) The transient switching simulation results presented in this paper show that while ferroelectrics do have the potential to provide voltage amplification, and hence an enhanced response to gate voltages in the megahertz range, they will cease to provide this advantage in the gigahertz to terahertz range.

3) Ferroelectric materials must have a viscosity coefficient  $\rho$  less than 0.1  $\Omega \cdot$  m to achieve voltage amplification with a 1-ps rise time.

While the requirement for a very low  $\rho$  may make NCFETs unsuitable for high-speed processors, they may still find application in low-speed applications, such as low-power sensors or low-power embedded systems, where polarization switching, negative capacitance, and voltage amplification will still occur. For high-speed applications, work is required to find a material with a suitably low  $\rho$  (below 0.1  $\Omega \cdot$ m).

#### **APPENDIX**

We derive a minimum switching time for a ferroelectric capacitor regardless of the ferroelectric material used. For this analysis, as shown in Fig. 10, we consider a simplified circuit consisting of a voltage source  $v_{\rm IN}$ , resistor R, ferroelectric capacitor  $C_{\rm FE}$ , and linear capacitor  $C_{\rm MOS}$  in a series circuit, representing the relevant properties of a switching NCFET.

We can say that the negative capacitance of the ferroelectric capacitor has provided a benefit if the voltage across the linear capacitor is greater than the voltage of the source. For simplicity, we use the single-domain LK equation

$$\rho \frac{dP(t)}{dt} = E_{\text{ext}}(t) - 2\alpha P(t) - 4\beta P^{3}(t) - 6\gamma P^{5}(t)$$

(7)

and consolidate the polarization polynomial into a single variable  $E_{int}(t)$  with units of V/m

$$\rho \frac{dP(t)}{dt} = E_{\text{ext}}(t) - E_{\text{int}}(t)$$

(8)

where  $E_{\rm ext}(t)$  is the applied electric field across the ferroelectric capacitor and  $E_{\rm int}(t) = 2\alpha P(t) + 4\beta P^3(t) + 6\gamma P^5(t)$ .

We now consider a single switching cycle, with  $v_{\rm IN}$  increasing from 0 to a constant voltage  $V_S > 0$ , which eventually causes the ferroelectric capacitor to flip, and hence an amplified voltage to appear across the linear capacitor. During this process, we know that the maximum applied electric field must be below  $V_S/t_{FE}$ , i.e.,  $E_{ext}(t) \leq V_S/t_{FE}$  for all t, because the ferroelectric capacitor cannot have more voltage across it than the source supplies. We assume that the maximum magnitude of the internal field remains below the coercive electric field  $E_C$  [31], i.e., the field required to flip the polarization; hence,  $|E_{\rm int}(t)| \leq E_C$ , which is a necessary condition for the ferroelectric to provide voltage amplification [3]. The coercive electric field  $E_C$  must also be lower in magnitude than  $V_S/t_{FE}$ , because we have assumed that  $V_S$  is large enough to flip the ferroelectric capacitor. Therefore, the maximum magnitude of the internal field is also below  $V_S/t_{FE}$ , i.e.,  $|E_{int}(t)| \leq V_S/t_{FE}$ . Thus, we can derive a maximum value for  $E_{\text{ext}}(t) - E_{\text{int}}(t)$ of  $2V_S/t_{FE}$  in the presumed switching cycle, occurring when a maximum  $E_{\text{ext}}(t) = V_S/t_{\text{FE}}$  is applied to flip the ferroelectric while  $E_{\text{int}}(t) = -V_S/t_{\text{FE}}$  retains its maximum magnitude but

$$\rho \left. \frac{dP(t)}{dt} \right|_{\text{max}} = [E_{\text{ext}}(t) - E_{\text{int}}(t)]_{\text{max}} = 2 \frac{V_S}{t_{\text{FE}}}.$$

(9)

We can also make an approximation on the charge accumulated on the ferroelectric capacitor

$$Q(t) = \int \left[ \varepsilon_0 \frac{v_{\rm FE}(t)}{t_{\rm FF}} + P(t) \right] dA \approx P(t)A$$

(10)

since for negative-capacitance operation, polarization must dominate the total charge contribution.

From the bounding values specified by (9) and (10), we can find the maximum current flowing through the circuit at any time

$$I_{\text{max}} = \frac{dQ(t)}{dt}|_{\text{max}} = A\frac{dP(t)}{dt}|_{\text{max}} = \frac{2AV_S}{\rho t_{\text{EF}}}.$$

(11)

If we determine how long it takes for a constant current of this magnitude to charge up the linear capacitor to a voltage of  $V_S$ , we will find the minimum time required for the ferroelectric capacitor to provide voltage amplification

$$\tau_{\min} = \frac{CV_S}{I_{\max}} = \frac{\rho t_{\text{FE}}}{2} \left(\frac{C_{\text{MOS}}}{A}\right). \tag{12}$$

#### REFERENCES

- [1] S. Borkar, "Design challenges of technology scaling," *IEEE Micro*, vol. 19, no. 4, pp. 23–29, Jul./Aug. 1999.

- [2] V. V. Zhirnov, R. K. Cavin, J. A. Hutchby, and G. I. Bourianoff, "Limits to binary logic switch scaling—A gedanken model," *Proc. IEEE*, vol. 91, no. 11, pp. 1934–1939, Nov. 2003.

- [3] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Lett.*, vol. 8, no. 2, pp. 405–410, Dec. 2007.

- [4] D. Jiménez, E. Miranda, and A. Godoy, "Analytic model for the surface potential and drain current in negative capacitance fieldeffect transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2405–2409, Oct. 2010.

- [5] K. Majumdar, S. Datta, and S. P. Rao, "Revisiting the theory of ferroelectric negative capacitance," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 2043–2049, May 2016.

- [6] J. H. Park and S. K. Joo, "Sub-kT/q subthreshold slope p-metal-oxide-semiconductor field-effect transistors with single-grained Pb(Zr,Ti)O<sub>3</sub> featuring a highly reliable negative capacitance," *Appl. Phys. Lett.*, vol. 108, no. 10, Mar. 2016, Art. no. 103504.

- [7] P. Chandra and P. B. Littlewood, "A Landau primer for ferroelectrics," in *Physics of Ferroelectrics: A Modern Perspective*, 1st ed. Heidelberg, Germany: Springer, 2007, pp. 69–116.

- [8] R. Resta, "Macroscopic polarization in crystalline dielectrics: The geometric phase approach," Rev. Mod. Phys., vol. 66, no. 3, pp. 899–915, Jul. 1994.

- [9] R. Vogel and P. J. Walsh, "Negative capacitance in amorphous semiconductor chalcogenide thin films," *Appl. Phys. Lett.*, vol. 14, no. 7, pp. 216–218, Feb. 1969.

- [10] M. Ershov, H. C. Liu, L. Li, M. Buchanan, Z. R. Wasilewski, and A. K. Jonscher, "Negative capacitance effect in semiconductor devices," *IEEE Trans. Electron Devices*, vol. 45, no. 10, pp. 2196–2206, Oct. 1998.

- [11] G. S. Nadkarni, N. Sankarraman, and S. Radharkrishnan, "Switching and negative capacitance in Al-Ge<sub>15</sub>Te<sub>81</sub>Sb<sub>2</sub>S<sub>2</sub>-Al devices," *J. Phys. D, Appl. Phys.*, vol. 16, no. 5, pp. 897–908, May 1983.

- [12] X. Wu, H. L. Evans, and E. S. Yang, "Negative capacitance at metal-semiconductor interfaces," *J. Appl. Phys.*, vol. 68, no. 6, pp. 2845–2848, May 1990.

- [13] R. Merlin and D. A. Kessler, "Photoexcited quantum wells: Nonlinear screening, bistability, and negative differential capacitance," *Phys. Rev. B*, vol. 41, no. 14, pp. 9953–9957, May 1990.

- [14] H. H. P. Gommans, M. Kemerink, and R. A. J. Janssen, "Negative capacitances in low-mobility solids," *Phys. Rev. B*, vol. 72, no. 23, Dec. 2005, Art. no. 235204.

- [15] S.-J. Chang and J.-G. Hwu, "Comprehensive study on negative capacitance effect observed in MOS(n) capacitors with ultrathin gate oxides," *IEEE Trans. Electron Devices*, vol. 58, no. 3, pp. 684–690, Mar. 2011.

- [16] A. I. Khan et al., "Negative capacitance in a ferroelectric capacitor," Nature Mater., vol. 14, no. 2, pp. 182–186, Feb. 2015.

- [17] M. H. Lee *et al.*, "Prospects for ferroelectric HfZrO<sub>X</sub> FETs with experimentally CET = 0.98 nm, SS<sub>for</sub> = 42 mV/dec, SS<sub>rev</sub> = 28 mV/dec, switch-off <0.2 V, and hysteresis-free strategies," in *Proc. IEEE Electron Devices Meeting*, Washington, DC, USA, Dec. 2015, pp. 22.5.1–22.5.4.

- [18] K.-S. Li et al., "Sub-60 mV-swing negative-capacitance FinFET without hysteresis," in Proc. IEEE Electron Devices Meeting, Washington, DC, USA, Dec. 2015, pp. 22.6.1–22.6.4.

- [19] A. I. Khan et al., "Negative capacitance in short-channel FinFETs externally connected to an epitaxial ferroelectric capacitor," IEEE Electron Device Lett., vol. 37, no. 1, pp. 111–114, Jan. 2016.

- [20] J. Li, B. Nagaraj, H. Liang, W. Cao, C. H. Lee, and R. Ramesh, "Ultrafast polarization switching in thin-film ferroelectrics," *Appl. Phys. Lett.*, vol. 84, no. 7, pp. 1174–1176, Feb. 2004.

- [21] A. I. Khan, C. W. Yeung, C. Hu, and S. Salahuddin, "Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation," in *Proc. IEEE Electron Devices Meeting*, Washington, DC, USA, Dec. 2011, pp. 11.3.1–11.3.4.

- [22] Cadence Version ic06.15.162, Cadence Design Syst., San Jose, CA, USA, 2012.

- [23] L. D. Landau and I. M. Khalatnikov, "On the anomalous absorption of sound near a second order phase transition point," *Dokl. Akad. Nauk* SSSR, vol. 96, pp. 469–472, Jun. 1954.

- [24] V. Fridkin, M. Kuehn, and H. Kliem, "The Weiss model and the Landau–Khalatnikov model for the switching of ferroelectrics," *Phys. B*, *Condens. Matter*, vol. 407, no. 12, pp. 2211–2214, Jun. 2012.

- [25] L.-Q. Chen, "APPENDIX A—Landau free-energy coefficients," in Physics of Ferroelectrics: A Modern Perspective, 1st ed. Heidelberg, Germany: Springer, 2007, pp. 363–372.

- [26] P. V. Lambeck and G. H. Jonker, "The nature of domain stabilization in ferroelectric perovskites," *J. Phys. Chem. Solids*, vol. 47, no. 5, pp. 453–461, Dec. 1986.

- [27] D. Ricinschi, C. Harnagea, C. Papusoi, L. Mitoseriu, V. Tura, and M. Okuyama, "Analysis of ferroelectric switching in finite media as a Landau-type phase transition," *J. Phys., Condens. Matter*, vol. 10, no. 2, pp. 477–492, Jan. 1998.

- [28] S. Sivasubramanian and A. Widom. (Aug. 2001). "Landau–Khalatnikov circuit model for ferroelectric hysteresis." [Online]. Available: http://arxiv.org/abs/cond-mat/0108189

- [29] S. Sivasubramanian, A. Widom, and Y. Srivastava, "Equivalent circuit and simulations for the Landau–Khalatnikov model of ferroelectric hysteresis," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 50, no. 8, pp. 950–957, Aug. 2003.

- [30] J. Junquera and P. Ghosez, "Critical thickness for ferroelectricity in perovskite ultrathin films," *Nature*, vol. 422, no. 6931, pp. 506–509, Apr. 2003.

- [31] M. N. A. Halif, S. Daud, and J. Osman, "Oscillatory dynamical switching system of bulk ferroelectrics," *Amer. J. Appl. Sci.*, vol. 2, no. 6, pp. 1073–1077, Jun. 2005.

**Zhi Cheng (Jason) Yuan** received the B.Sc. degree in engineering physics (nanoengineering option) from the University of Alberta, Edmonton, AB, Canada, in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include the simulation of high speed integrated circuits, with an emphasis on the modeling of ferroelectric negative-capacitance FETs.

**Shahriar Rizwan** received the B.Sc. degree in electrical and electronic engineering from the Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 2012. He is currently pursuing the Ph.D. degree in electrical engineering with the University of Alberta, Edmonton, AB, Canada.

He was a Software Engineer with the Samsung R&D Institute Bangladesh, Dhaka, from 2012 to 2014.

**Michael Wong** received the B.Sc. degree in computer engineering from the University of Alberta, Edmonton, AB, Canada, in 2013, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include the modeling and simulation of nanoscale devices, including FinFETs and 2-D FETs.

**Kyle Holland** received the B.Sc. degree in engineering physics (nanoengineering option) from the University of Alberta, Edmonton, AB, Canada, in 2009, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include the quantum simulation of carbonbased nanoelectronics, with an emphasis on modeling the high frequency performance of graphene devices.

**Sam Anderson** is currently pursuing the B.Sc. degree in engineering physics (nanoengineering option) with the University of Alberta, Edmonton, AB, Canada

He is interested in the technological and environmental adaptations that will impact human life in the 21st century. His current research interests include the use of novel materials in solar cell applications.

**Terence B. Hook** received the Sc.B. degree in electrical engineering from Brown University, Providence, RI, USA, in 1980, and the Ph.D. degree in electrical engineering from Yale University, New Haven, CT, USA, in 1986.

Since 1980, he has been with IBM, where he has been involved in technology development and research in Essex Junction, VT, USA, East Fishkill, NY, USA, and Albany, NY, USA.

**Diego Kienle** received his Ph.D. in theoretical physics from the Research Center Juelich and the University Saarland, Germany. After appointments at Purdue University and Sandia National Laboratories, he is currently with the Institute of Theoretical Physics at the University Bayreuth, Germany. His research interest include the theory and simulation of quantum kinetic transport in nanoscale materials and devices.

**Serag Gadelrab** received the Ph.D. degree from the University of Waterloo, Waterloo, ON, Canada.

He is currently the Director of Engineering with Qualcomm Canada Inc., Toronto, ON, Canada. His current research interests include network input—output controllers, chipset design methods, and high speed packet switch architectures.

**Prasad S. Gudem** (M'96) received the B.Tech. degree in electrical engineering from IIT Madras, Chennai, India, in 1988, and the Ph.D. degree in electrical engineering from the University of Waterloo, Waterloo, ON, Canada, in 1996

He is currently a Vice President of Engineering with the Analog/RF Integrated Circuit Design Group, Qualcomm Technologies Inc., San Diego, CA, USA.

Mani Vaidyanathan received the Ph.D. degree in electrical engineering from the University of British Columbia, Vancouver, BC, Canada.

He is currently an Associate Professor with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB, Canada. His research interests include the modeling, simulation, and understanding of electronic devices for future electronics, with a present focus on the radio-frequency performance of FinFETs and 2-D materials.