US009252827B2

# (12) United States Patent

Gudem et al.

(10) Patent No.:

US 9,252,827 B2

(45) **Date of Patent:**

Feb. 2, 2016

## (54) SIGNAL SPLITTING CARRIER AGGREGATION RECEIVER ARCHITECTURE

(75) Inventors: Prasad Srinivasa Siva Gudem, San

Diego, CA (US); **Udara C. Fernando**, San Diego, CA (US); **Li-Chung Chang**,

Irvine, CA (US)

(73) Assignee: QUALCOMM Incorporated, San

Diego, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 86 days.

(21) Appl. No.: 13/411,461

(22) Filed: Mar. 2, 2012

(65) Prior Publication Data

US 2012/0327825 A1 Dec. 27, 2012

# Related U.S. Application Data

(60) Provisional application No. 61/501,381, filed on Jun. 27, 2011.

(51) **Int. Cl. H04B 1/3805**

**H04B 1/3805** (2015.01) **H04B 1/00** (2006.01)

(52) U.S. Cl.

(58) Field of Classification Search

See application file for complete search history.

# (56) References Cited

### U.S. PATENT DOCUMENTS

3,911,364 A 10/1975 Langseth et al. 4,035,728 A 7/1977 Ishikawa et al.

4,035,729 A 7/1977 Perry 4,246,655 A 1/1981 Parker 4,326,294 A 4/1982 Okamoto et al. (Continued)

### FOREIGN PATENT DOCUMENTS

CN 1523912 A 8/2004 CN 1922795 A 2/2007 (Continued)

### OTHER PUBLICATIONS

Aparin et al., "A Highly-integrated tri-band/quad-mode SiGe BiCMOS RF-to-baseband and receiver for wireless CDMA/WCDMA/AMPS applications with GPS capability", Solid-State Circuits Conference, 2002. Digest of Technical Papers. 2002 IEEE International Feb. 3-7, 2002, Piscataway, NJ, USA, IEEE, vol. 1, 2002, pp. 234-235, XP010585547, ISBN: 0-7803-7335-9.

(Continued)

Primary Examiner — Khaled Kassim

Assistant Examiner — Zhaohui Yang

(74) Attorney, Agent, or Firm — James T. Gutierrez

# (57) ABSTRACT

A wireless communication device configured for receiving a multiple carrier signal is described. The wireless communication device includes a primary signal splitting carrier aggregation architecture. The primary signal splitting carrier aggregation architecture includes a primary antenna and a transceiver chip. The primary signal splitting carrier aggregation architecture reuses a first diversity/simultaneous hybrid dual receiver path. The wireless communication device also includes a secondary signal splitting carrier aggregation architecture. The secondary signal splitting carrier aggregation architecture includes a secondary antenna and a receiver chip. The secondary signal splitting carrier aggregation architecture reuses a second diversity/simultaneous hybrid dual receiver path.

## 40 Claims, 15 Drawing Sheets

# US 9,252,827 B2 Page 2

| (56) References Cited  |        |                    |                                   | 7,570,111 B1                        | 8/2009            | Vagher et al.                                 |

|------------------------|--------|--------------------|-----------------------------------|-------------------------------------|-------------------|-----------------------------------------------|

| (00)                   |        |                    |                                   | 7,599,675 B2                        | 10/2009           | Mu et al.                                     |

|                        | U.S. 1 | PATENT             | DOCUMENTS                         | 7,643,847 B2                        |                   | Daanen et al.                                 |

| 4.715.040              |        | 12/1007            | Management                        | 7,643,848 B2<br>7,697,905 B2        |                   | Robinett<br>Lee et al.                        |

| 4,715,048<br>4,742,563 |        |                    | Masamura<br>Fukumura              | 7,728,664 B2                        |                   | Chang et al.                                  |

| 4,756,023              |        |                    | Kojima                            | 7,751,513 B2                        | 7/2010            | Eisenhut et al.                               |

| 4,969,207              |        |                    | Sakamoto et al.                   | 7,764,726 B2                        |                   | Simic et al.                                  |

| 5,056,411              |        |                    | Baker                             | 7,848,724 B2<br>7,869,528 B2        |                   | Bult et al.<br>Robinson                       |

| 5,128,630<br>5,291,519 |        |                    | Mijuskovic<br>Tsurumaru           | 7,877,075 B1                        |                   | Jin et al.                                    |

| 5,321,850              |        |                    | Backstrom et al.                  | 7,911,269 B2                        |                   | Yang et al.                                   |

| 5,345,601              | Α      | 9/1994             | Takagi et al.                     | 7,944,298 B2                        |                   | Cabanillas et al.                             |

| 5,390,342              |        |                    | Takayama et al.                   | 7,949,309 B2<br>7,952,398 B2        |                   | Rofougaran et al.<br>Salcido et al.           |

| 5,559,838<br>5,566,364 |        |                    | Nakagoshi<br>Mizoguchi et al.     | 8,022,772 B2                        |                   | Cassia et al.                                 |

| 5,694,396              |        |                    | Firouzbakht et al.                | 8,055,229 B2                        | 11/2011           |                                               |

| 5,697,083              |        | 12/1997            | Sano                              | 8,063,706 B2                        | 11/2011           |                                               |

| 5,761,613              |        |                    | Saunders et al.                   | 8,081,672 B2<br>8,090,332 B2        |                   | Kent et al.<br>Sahota et al.                  |

| 5,794,159<br>5,805,643 |        | 8/1998             | Portin<br>Seki et al.             | 8,090,369 B2                        |                   | Kitazoe                                       |

| 5,805,989              |        |                    | Ushida                            | 8,139,670 B1                        | 3/2012            | Son et al.                                    |

| 5,835,853              |        |                    | Enoki et al.                      | 8,149,955 B2                        | 4/2012            |                                               |

| 5,940,452              |        | 8/1999             |                                   | 8,195,117 B2<br>8,208,887 B2        |                   | Bult et al.<br>Lee et al.                     |

| 5,999,815<br>5,999,990 |        | 12/1999<br>12/1999 | TenBrook et al.<br>Sharrit et al. | 8,217,723 B2                        |                   | Rajendran et al.                              |

| 6,026,288              |        |                    | Bronner                           | 8,242,841 B2                        | 8/2012            |                                               |

| 6,040,732              |        |                    | Brokaw                            | 8,270,927 B2                        |                   | Wallace et al.                                |

| 6,044,254              |        |                    | Ohta et al.                       | 8,290,449 B2<br>8,295,778 B2        |                   | Keehr et al.<br>Kotecha et al.                |

| 6,063,961<br>6,069,923 |        |                    | Kroner<br>Ostman et al.           | 8,306,494 B2                        | 11/2012           |                                               |

| 6,088,348              |        |                    | Bell, III et al.                  | 8,442,473 B1                        |                   | Kaukovuori et al.                             |

| 6,208,844              |        |                    | Abdelgany                         | 8,514,015 B2                        | 8/2013            |                                               |

| 6,249,687              |        |                    | Thomsen et al.                    | 8,571,510 B2<br>8,600,315 B2        |                   | Liu et al.<br>Roufoogaran et al.              |

| 6,407,689              |        |                    | Bazarjani et al.<br>Schollhorn    | 8,626,084 B2                        |                   | Chan et al.                                   |

| 6,424,683<br>6,430,237 |        | 8/2002             |                                   | 8,676,148 B2                        |                   | Ogasawara                                     |

| 6,472,947              |        | 10/2002            |                                   | 8,706,069 B2                        |                   | Khoini-Poorfard et al.                        |

| 6,473,601              |        | 10/2002            |                                   | 2002/0008575 A1                     |                   | Oskowsky et al.<br>Adachi et al.              |

| 6,522,895              |        |                    | Montalvo                          | 2002/0061773 A1<br>2002/0111163 A1  |                   | Hamabe                                        |

| 6,535,725<br>6,600,759 |        | 7/2003             | Hatcher et al.                    | 2002/0132597 A1                     |                   | Peterzell et al.                              |

| 6,600,907              |        |                    | Taguchi                           | 2002/0173337 A1                     |                   | Hajimiri et al.                               |

| 6,600,931              |        |                    |                                   | 2002/0193108 A1<br>2003/0076797 A1  |                   | Robinett<br>Lozano                            |

| 6,657,498              |        |                    | Park et al.<br>Franca-Neto        | 2003/00/6/9/ A1<br>2003/0081694 A1  | 5/2003            |                                               |

| 6,806,777<br>6,819,941 |        |                    | Dening et al.                     | 2003/0125040 A1                     |                   | Walton et al.                                 |

| 6,888,888              |        |                    | Tu et al.                         | 2003/0148750 A1                     |                   | Yan et al.                                    |

| 6,952,594              |        | 10/2005            |                                   | 2003/0157915 A1<br>2003/0176176 A1  | 8/2003            | Atkinson et al.<br>Leinonen et al.            |

| 6,954,446<br>6,983,132 |        | 10/2005            | Kuffner<br>Woo et al.             | 2003/01/01/0 A1<br>2003/0203743 A1  |                   | Sugar et al.                                  |

| 6,985,712              |        |                    | Yamakawa et al.                   | 2003/0206076 A1                     |                   | Hashemi et al.                                |

| 6,987,950              |        | 1/2006             | Coan                              | 2003/0228851 A1                     |                   | Taniguchi                                     |

| 7,013,166              |        |                    | Clifford                          | 2004/0087290 A1<br>2004/0092243 A1  |                   | Schmidt et al.<br>Hey-Shipton                 |

| 7,023,272<br>7,024,172 |        |                    | Hung et al.<br>Murphy et al.      | 2004/0032243 A1<br>2004/0113746 A1  |                   | Brindle                                       |

| 7,039,377              |        | 5/2006             |                                   | 2004/0116086 A1                     |                   | Huttunen                                      |

| 7,123,891              | B2     | 10/2006            | Loke                              | 2004/0121753 A1                     |                   | Sugar et al.                                  |

| 7,142,042              |        | 11/2006            |                                   | 2004/0204104 A1<br>2004/0219959 A1  |                   | Horng et al.<br>Khayrallah et al.             |

| 7,161,423<br>7,167,044 |        |                    | Paul et al.<br>Li et al.          | 2004/0224643 A1                     | 11/2004           |                                               |

| 7,187,239              |        | 3/2007             |                                   | 2004/0253955 A1                     |                   | Love et al.                                   |

| 7,187,735              | B2     | 3/2007             | Kent, III et al.                  | 2004/0266356 A1                     |                   | Javor et al.                                  |

| 7,187,904              |        |                    | Gainey et al.                     | 2005/0039060 A1<br>2005/0075077 A1  |                   | Okayasu<br>Mach et al.                        |

| 7,212,788<br>7,224,231 |        | 5/2007             | Weber et al.                      | 2005/0079847 A1                     | 4/2005            |                                               |

| 7,260,377              |        |                    | Burns et al.                      | 2005/0118977 A1                     |                   | Drogi et al.                                  |

| 7,283,851              | B2     | 10/2007            | Persico et al.                    | 2005/0197090 A1*<br>2005/0215264 A1 |                   | Stockstad et al 455/313<br>Subramaniam et al. |

| 7,299,021              |        |                    | P rssinen et al.                  | 2005/0215264 A1<br>2005/0265084 A1  | 9/2005<br>12/2005 |                                               |

| 7,313,368<br>7,317,894 |        | 1/2007             | Wu et al.<br>Hirose               | 2005/0203084 A1<br>2005/0277387 A1  |                   | Kojima et al.                                 |

| 7,333,831              |        |                    | Srinivasan et al.                 | 2006/0009177 A1                     | 1/2006            | Persico et al.                                |

| 7,356,325              | B2*    | 4/2008             | Behzad et al 455/323              | 2006/0023745 A1                     |                   | Koo et al.                                    |

| 7,372,336              |        |                    | Lee et al.                        | 2006/0061773 A1                     |                   | Lee et al.                                    |

| 7,403,508              |        | 7/2008             |                                   | 2006/0121937 A1<br>2006/0128322 A1  | 6/2006            | Son<br>Igarashi et al.                        |

| 7,444,166<br>7,454,181 |        | 10/2008            | Banister et al.                   | 2006/0128322 A1<br>2006/0146693 A1  |                   | Mori et al.                                   |

| 7,477,106              |        |                    | Van Bezooijen et al.              | 2006/0189286 A1                     | 8/2006            | Kyu et al.                                    |

| 7,486,135              |        | 2/2009             | 3                                 | 2006/0222100 A1                     | 10/2006           |                                               |

|                        |        |                    |                                   |                                     |                   |                                               |

# US 9,252,827 B2

Page 3

| (56)                                | Referen           | ices Cited                           |       | 2011/0292844<br>2011/0299434 |                                |              | Kwun et al.<br>Gudem et al.              |

|-------------------------------------|-------------------|--------------------------------------|-------|------------------------------|--------------------------------|--------------|------------------------------------------|

| U.S.                                | PATENT            | DOCUMENTS                            |       | 2011/0300810                 | A1 12/                         | 2011         | Mikhemar et al.                          |

| 2006/0224662 44                     | 10/2006           | D'1-1                                |       | 2012/0009886<br>2012/0013387 |                                |              | Poulin<br>Sankaranarayanan et al.        |

| 2006/0234662 A1<br>2006/0291428 A1  |                   | Diloisy<br>Filipovic                 |       | 2012/0026862                 | A1 2/                          | 2012         | Sadri et al.                             |

| 2007/0049332 A1                     | 3/2007            | Higuchi                              |       | 2012/0044927<br>2012/0056681 |                                | 2012<br>2012 | Pan et al.                               |

| 2007/0060080 A1<br>2007/0072577 A1  |                   | Nishimura et al.<br>Rozenblit et al. |       | 2012/0057621                 |                                |              | Hong et al.                              |

| 2007/0105517 A1                     |                   | Chang et al.                         |       | 2012/0195237                 |                                |              | Chan et al.                              |

| 2007/0142013 A1<br>2007/0177656 A1  |                   | Bucknor et al.  Maruta et al.        |       | 2012/0236829<br>2012/0293265 |                                |              | Takano et al.<br>Heikkinen et al.        |

| 2007/0177693 A1*                    |                   | Kluge 375/                           | /332  | 2012/0294299                 | A1 11/                         | 2012         | Fernando                                 |

| 2007/0184801 A1                     | 8/2007            | Kogawa et al.                        |       | 2012/0327825<br>2012/0329395 |                                |              | Gudem et al.<br>Husted et al.            |

| 2007/0197170 A1<br>2007/0197178 A1  | 8/2007<br>8/2007  |                                      |       | 2013/0003617                 |                                |              | Gudem et al.                             |

| 2007/0197204 A1                     | 8/2007            | Herczog et al.                       |       | 2013/0003783                 |                                |              | Gudem et al.                             |

| 2007/0202890 A1<br>2007/0242784 A1  | 8/2007<br>10/2007 | Feher<br>Sampson et al.              |       | 2013/0043946<br>2013/0051284 |                                |              | Hadjichristos et al.<br>Khlat            |

| 2007/0243832 A1                     |                   | Park et al.                          |       | 2013/0114769                 |                                |              | Fernando                                 |

| 2007/0262817 A1<br>2007/0262871 A1  |                   | Ciccarelli et al.                    |       | 2013/0163492<br>2013/0217398 | A1 6/                          | 2013<br>2013 | Wong<br>Winiecki et al.                  |

| 2007/0202871 A1<br>2008/0004078 A1  |                   | Yamagajo et al.<br>Barratt et al.    |       | 2013/0230080                 | A1 9/                          | 2013         | Gudem et al.                             |

| 2008/0013654 A1                     |                   | Rick et al.                          |       | 2013/0231064<br>2013/0265892 |                                |              | Gudem et al.<br>Fernando                 |

| 2008/0117999 A1<br>2008/0139151 A1  |                   | Kadous et al.<br>Ojo et al.          |       | 2013/0203832                 |                                |              | Tasic et al.                             |

| 2008/0204148 A1                     | 8/2008            | Kim et al.                           |       | 2013/0316668<br>2013/0316669 |                                |              | Davierwalla et al.<br>Davierwalla et al. |

| 2008/0224770 A1<br>2008/0224791 A1  |                   | Kim et al.<br>Cheng                  |       | 2013/0316670                 |                                |              | Tasic et al.                             |

| 2008/0225971 A1                     |                   | Behzad                               |       | 2013/0329665                 |                                |              | Kadous et al.                            |

| 2008/0261650 A1<br>2009/0124227 A1  |                   | Piriyapoksombut et al.<br>Ishiguro   |       | 2014/0072001<br>2014/0113578 |                                | 2014<br>2014 | Chang et al.                             |

| 2009/0124227 A1<br>2009/0227214 A1  |                   | Georgantas et al.                    |       | 2014/0269853                 |                                |              | Gudem et al.                             |

| 2009/0237161 A1                     | 9/2009            | Fagg<br>Sanderford, Jr.              |       |                              |                                |              |                                          |

| 2009/0243869 A1<br>2009/0253456 A1  |                   | Toh et al.                           |       | FO                           | REIGN I                        | AIE          | NT DOCUMENTS                             |

| 2009/0290659 A1                     |                   | Petrovic et al.                      |       |                              | 101228702                      | 2 A          | 7/2008                                   |

| 2009/0323779 A1<br>2010/0019970 A1  |                   | Lennen<br>Farrokhi et al.            |       |                              | 101242158<br>101523967         |              | 8/2008<br>9/2009                         |

| 2010/0034094 A1                     | 2/2010            |                                      |       |                              | 101789805                      |              | 7/2010                                   |

| 2010/0040178 A1<br>2010/0142440 A1* |                   | Sutton et al. Inoue                  | /2.70 | EP<br>EP                     | 1164719<br>1370012             |              | 12/2001<br>12/2003                       |

| 2010/0195754 A1                     | 8/2010            | Li et al.                            |       | EP                           | 1398887                        |              | 3/2004                                   |

| 2010/0197263 A1<br>2010/0210226 A1  |                   | Dwyer et al.<br>Matsuyama            |       | EP                           | 1708372                        |              | 10/2006                                  |

| 2010/0210272 A1                     | 8/2010            | Sundstrom et al.                     |       | EP<br>EP                     | 1726098<br>1748567             |              | 11/2006<br>1/2007                        |

| 2010/0210299 A1<br>2010/0214184 A1  |                   | Gorbachov<br>Tran et al.             |       | EP                           | 1761076                        |              | 3/2007                                   |

| 2010/0225414 A1                     | 9/2010            | Gorbachov                            |       | EP<br>EP                     | 2068583<br>2141818             |              | 6/2009<br>1/2010                         |

| 2010/0226327 A1<br>2010/0232493 A1  |                   | Zhang et al.<br>Thirumoorthy         |       | EP                           | 1916767                        |              | 12/2010                                  |

| 2010/0237947 A1                     | 9/2010            | Xiong et al.                         |       | EP<br>EP                     | 2393205<br>2398285             |              | 12/2011<br>12/2011                       |

| 2010/0253435 A1<br>2010/0265875 A1  |                   | Ichitsubo et al. Zhao et al.         |       | GB                           | 2472978                        | 3 A          | 3/2011                                   |

| 2010/0203873 A1<br>2010/0271986 A1  | 10/2010           |                                      |       | JP<br>JP                     | 05227234<br>H0730452           |              | 9/1993<br>1/1995                         |

| 2010/0272051 A1                     |                   | Fu et al.<br>Borremans               |       | JΡ                           | 07221684                       | ļ            | 8/1995                                   |

| 2010/0301946 A1<br>2010/0311378 A1  |                   | Tasic et al.                         |       | JP<br>JP                     | 9027778<br>09116458            |              | 1/1997<br>5/1997                         |

| 2010/0328155 A1                     |                   | Simic et al.                         | ,     | JP H                         | H11127300                      |              | 5/1999                                   |

| 2010/0330977 A1<br>2011/0018635 A1  |                   | Kadous et al. Tasic et al.           |       |                              | )00013278<br>)01285114         |              | 1/2000<br>10/2001                        |

| 2011/0044380 A1                     |                   | Marra et al.                         |       |                              | 00126311-                      |              | 9/2002                                   |

| 2011/0050319 A1<br>2011/0084791 A1  | 3/2011<br>4/2011  | Mun et al.                           |       |                              | )04015162<br>)06520143         |              | 1/2004<br>8/2006                         |

| 2011/0086603 A1                     |                   | Toosi et al.                         |       |                              | 007324711                      |              | 12/2007                                  |

| 2011/0110463 A1<br>2011/0122972 A1  |                   | Chang et al.<br>Lie et al.           |       |                              | 008085793                      |              | 4/2008                                   |

| 2011/0165848 A1                     | 7/2011            | Gorbachov et al.                     |       |                              | )0851953 <i>5</i><br>)09027778 |              | 6/2008<br>2/2009                         |

| 2011/0193625 A1<br>2011/0194504 A1  |                   | Gatta et al.<br>Gorokhov et al.      |       |                              | 009130867                      |              | 6/2009                                   |

| 2011/0204973 A1                     | 8/2011            | Hu et al.                            |       |                              | )11015112<br>)11082669         |              | 1/2011<br>4/2011                         |

| 2011/0211533 A1<br>2011/0217945 A1  |                   | Casaccia et al.<br>Uehara et al.     |       | JP 20                        | 011091747                      | Α            | 5/2011                                   |

| 2011/0222443 A1                     | 9/2011            | Khlat                                |       |                              | 011119807<br>O0150636          |              | 6/2011<br>7/2001                         |

| 2011/0222444 A1                     |                   | Khlat et al.                         | ,     | WO                           | 0237686                        | 5            | 5/2002                                   |

| 2011/0242999 A1<br>2011/0250926 A1  |                   | Palanki et al.<br>Wietfeldt et al.   |       |                              | )05039060<br>)05062477         |              | 4/2005<br>7/2005                         |

| 2011/0268048 A1                     | 11/2011           | Toskala et al.                       |       | WO WO20                      | 005064816                      | A1           | 7/2005                                   |

| 2011/0268232 A1                     | 11/2011           | Park et al.                          | -     | WO 20                        | 005088847                      | A1           | 9/2005                                   |

| (56)                                     | References Cited                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | FOREIGN PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                          |

| WO W | 2006050515 A2 5/2006<br>2006118538 A2 11/2006<br>2008059257 A1 5/2008<br>2008084539 A1 7/2008<br>2008092745 A1 8/2008<br>2008103757 8/2008<br>2008145604 A1 12/2008<br>2010059257 A1 5/2010<br>2011019850 A1 2/2011<br>2011050729 A1 5/2011<br>2011050729 A1 8/2011<br>2011092005 A1 8/2011<br>2011138697 A1 11/2011<br>2012008705 A2 1/2012<br>2012049529 A1 4/2012<br>2013036794 A1 3/2013<br>2013131047 9/2013 |

| ""                                       | OTHER RIDI ICATIONS                                                                                                                                                                                                                                                                                                                                                                                               |

### OTHER PUBLICATIONS

Hwang, et al., "A High IIP2 Direct-Conversion Receiver using Even-Harmonic Reduction Technique for Cellular CDMA/PCS/GPS applications," IEEE Transaction on Circuits and Systems.

MSM6500 Chipset Solution, Qualcomm Incorporated.

Sever et al. "A Dual-Antenna Phase-Array Ultra-Wideband CMOS Transceiver". IEEE Communications Magazine [Online] 2006, vol. 44, Issue 8, pp. 102-110. See pp. 104-107.

Winternitz, et al., "A GPS Receiver for High-Altitude Satellite Navigation," IEEE Journal of Selected Topics in Signal Processing, vol. 3, No. 4, pp. 541-556, Aug. 2009.

3GPP TS 36.101 V11.0.0, 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE) radio transmission and reception (Release 11), Mar. 2012

Broyde F., et al., "The Noise Performance of aMultiple-Input-Port and Multiple-Output-Port Low-Noise Amplifier Connected to an Array of Coupled Antennas," International Journal of Antennas and Propagation, vol. 2011, Article ID 438478, Jul. 18, 2011, 12 pages. Chen, et al, "A 5-6 GHz 1-V CMOS Direct-Conversion Receiver With an Integrated Quadrature Coupler," IEEE Journal of Solid-State Circuits, vol. 42, No. 9, 2007, pp. 1963-1975.

Chen, et al., "A monolithic 5.9-GHz CMOS I/Q direct-down converter utilizing a quadrature coupler and transformer-coupled subharmonic mixers," Microwave and Wireless Components Letters, IEEE, vol. 16, No. 4, 2006, pp. 197-199

Garuda, et al., "A Multi-band CMOS RF Front-end for 4G WiMAX and WLAN Applications," 2006 IEEE International Symposium on Circuits and Systes, 2006. ISCAS 2006. May 2006, 4 pages

Hashemi, et al., "Concurrent Multiband Low-Noise Amplifiers-Theory, Design, and Applications," IEEE Transactions on Microwave Theory and Techniques, vol. 50, No. 1, Jan. 2002.

Henrik M et al., "A Full Duplex Front End Module for WiFi 802.11.n. Applications", European Microwave Association, vol. 12, No. 4, Oct. 2008, pp. 162-165.

International Search Report and Written Opinion—PCT/US2012/

044473—ISA/EPO—Jan. 15, 2013. Jones W. W., et al., "Narrowband interference suppression using filter-bank analysis/synthesis techniques", Military Communications Conference, 1992. MILCOM '92, Conference Recor D. Communications-Fusing Command, Control and Intelligence., IEEE San Diego, CA, USA, Oct. 11-14, 1992, New York, NY, USA, IEEE, US, Oct. 11, 1992, pp. 898-902, XP010060840, DOI: 10.1109/ MILCOM.1992.243977, ISBN: 978-0-7803-0585-4.

Jussi R et al., "A Dual-Band RF Front-End for WCDMA and GSM Applications", IEEE, Journal Solid-State Circuits, 2001, vol. 36, No. 8, pp. 1198-1204.

Kevin W et al., "3G/4G Multimode Cellular Front End Challenges", Part 2: Architecture Discussion, RFMD® White Paper, 9 pages

Kim, T.W., et al., Highly Linear Receiver Front-End Adopting MOSFET Transconductance Linearization by Multiple Gated Transistors, IEEE Journal of Solid-State Circuits, United States, IEEE, Jan. 1, 2004, vol. 39, No. 1, pp. 223-229.

Lai, C.M.,et al., "Compact router transceiver architecture for carrier aggregation systems", Microwave Conference (EUMC), 2011 41st European, IEEE, Oct. 10, 2011, pp. 693-696, XP032072825, ISBN: 978-1-61284-235-6 the whole document.

Lee et al., "Development of Miniature Quad SAW filter bank based on PCB substrate", IEEE Intl Frequency Control Symp, pp. 146-149,

MSM6000 Chipset Solution, Qualcomm Incorporated.

Philips: "Capabilities of multi-transceiver UES", 3GPP Draft; R1-103913, 3rd Generation Partnership Project (3GPP), Mobile Competence Centre; 650, Route Des Lucioles; F-06921 Sophia-Antipolis Cedex; France, vol. RAN WG1, No. Dresden, Germany; 20100628, Jun. 22, 2010, XP050449298, [retrieved on Jun. 22, 2010] the whole document

Pitschi M. et al., "High Performance Microwave Acoustic Components for Mobile Radios", Ultrasonics Symposium (IUS), 2009 IEEE International, EPCOS AG, Munich, Germany, vol. 1, Sep. 20-23,

Qualcomm Europe: "UE Implementation Impact due to 4C-HSDPA Operation", 3GPP Draft; R1-094067\_UE\_IMPL\_IMPACT\_4C\_ HSDPA, 3rd Generation Partnership Project (3GPP), Mobile Competence Centre; 650, Route Des Lucioles; F-06921 Sophia-Antipolis Cedex ; France, No. Miyazaki; 20091012, Oct. 12, 2009, XP050388547, [retrieved on Oct. 6, 2009].

Rahn D.G., et al., "A fully integrated multiband MIMO WLAN transceiver RFIC," IEEE J. Solid-State Circuits, 2005, vol. 40 (8), 1629-1641

Tasic A. et al., "Design of Adaptive Multimode RF Front-End Circuits", IEEE Journal of Solid-State Circuits, vol. 42, Issue 2, Feb. 2007 pp. 313-322.

"UMTS Picocell Front End Module", CTS Corp. 8 pages.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 15

# SIGNAL SPLITTING CARRIER AGGREGATION RECEIVER ARCHITECTURE

### RELATED APPLICATIONS

This application is related to and claims priority from U.S. Provisional Patent Application Ser. No. 61/501,381 filed Jun. 27, 2011, for "CURRENT STEERING CARRIER AGGREGATION RECEIVER ARCHITECTURE."

### TECHNICAL FIELD

The present disclosure relates generally to wireless devices for communication systems. More specifically, the present disclosure relates to systems and methods for a signal splitting carrier aggregation receiver architecture.

### **BACKGROUND**

Electronic devices (cellular telephones, wireless modems, computers, digital music players, Global Positioning System units, Personal Digital Assistants, gaming devices, etc.) have become a part of everyday life. Small computing devices are 25 now placed in everything from automobiles to housing locks. The complexity of electronic devices has increased dramatically in the last few years. For example, many electronic devices have one or more processors that help control the device, as well as a number of digital circuits to support the 30 processor and other parts of the device.

These electronic devices may communicate wirelessly with each other and with a network. As the demand for information by these electronic devices has increased, the downlink throughput has also increased. One such way to increase downlink throughput is the use of carrier aggregation. In carrier aggregation, multiple carriers may be aggregated on the physical layer to provide the required bandwidth (and thus the required throughput).

It may be desirable for an electronic device to maximize 40 battery life. Because an electronic device often runs on a battery with a limited operation time, reductions in the power consumption of an electronic device may increase the desirability and functionality of the electronic device.

The electronic devices have also become smaller and 45 cheaper. To facilitate both the decrease in size and the decrease in cost, additional circuitry and more complex circuitry are being used on integrated circuits. Thus, any reduction in the die area used by circuitry may reduce both the size and cost of an electronic device. Benefits may be realized by 50 improvements to electronic devices that allow an electronic device to participate in carrier aggregation while minimizing the cost and size of the electronic device while also minimizing the power consumption of the electronic device.

# **SUMMARY**

A wireless communication device configured for receiving a multiple carrier signal is described. The wireless communication device includes a primary signal splitting carrier 60 aggregation architecture that includes a primary antenna and a transceiver chip. The primary signal splitting carrier aggregation architecture reuses a first diversity/simultaneous hybrid dual receiver path. The wireless communication device also includes a secondary signal splitting carrier 65 aggregation architecture that includes a secondary antenna and a receiver chip. The secondary signal splitting carrier

2

aggregation architecture reuses a second diversity/simultaneous hybrid dual receiver path.

The primary signal splitting carrier aggregation architecture and the secondary signal splitting carrier aggregation architecture may not require four antennas, a power splitter, an external low noise amplifier or die-to-die signal routing. The transceiver chip may include a transmitter, a first primary receiver and a first secondary receiver. The receiver chip may include a second primary receiver and a second secondary receiver. Each receiver may include multiple low noise amplifiers for a first band and multiple low noise amplifiers for a second band. Each low noise amplifier may include a first stage amplifier and a second stage amplifier.

The first stage amplifier may be a transconductance stage and the second stage amplifier may be a cascode stage. In one configuration, the first band may be a low band and the second band may be a mid band. In another configuration, the first band may be a low band and the second band may be a high band. In yet another configuration, the first band may be a mid band and the second band may be a high band.

A first routing may be used from the primary antenna through the first primary receiver to obtain a first primary inphase/quadrature signal. A second routing may be used from the primary antenna through the first secondary receiver to obtain a first secondary inphase/quadrature signal. A third routing may be used from the secondary antenna through the second primary receiver to obtain a second primary inphase/quadrature signal. A fourth routing may be used from the secondary antenna through the second secondary receiver to obtain a second secondary inphase/quadrature signal.

The primary signal splitting carrier aggregation architecture and the secondary signal splitting carrier aggregation architecture may be in inter-band operation. The second routing may pass through a first signal splitting stage. The fourth routing may pass through a second signal splitting stage.

The first signal splitting stage may route a signal output from a first stage amplifier in a first band low noise amplifier of the first primary receiver to a second stage amplifier in a second band low noise amplifier of the first secondary receiver. The second signal splitting stage may route a signal output from a first stage amplifier in a first band low noise amplifier of the second primary receiver to a second stage amplifier in a second band low noise amplifier of the second secondary receiver.

The first signal splitting stage may route a signal output from a second stage amplifier in a first band low noise amplifier of the first primary receiver to a mixer in the first secondary receiver. The second signal splitting stage may route a signal output from a second stage amplifier in a first band low noise amplifier of the second primary receiver to a mixer in the second secondary receiver.

The primary signal splitting carrier aggregation architecture and the secondary signal splitting carrier aggregation architecture may be in intra-band operation. The second routing may pass through a first signal splitting stage. The fourth routing may pass through a second signal splitting stage. The first signal splitting stage may split a signal output from a first stage amplifier in a first band low noise amplifier of the first primary receiver, route the signal to a second stage amplifier in the first band low noise amplifier of the first primary receiver and route the signal to a second stage amplifier in a second band low noise amplifier of the first secondary receiver. The second signal splitting stage may split a signal output from a first stage amplifier in a first band low noise amplifier of the second primary receiver, route the signal to a second stage amplifier in the first band low noise amplifier of

the second primary receiver and route the signal to a second stage amplifier in a second band low noise amplifier of the second secondary receiver.

The first signal splitting stage may split a signal output from a second stage amplifier in a first band low noise amplifier of the first primary receiver, route the signal to a first mixer of the first primary receiver and route the signal to a second mixer of the second primary receiver. The second signal splitting stage may split a signal output from a second stage amplifier in a first band low noise amplifier of the second primary receiver, route the signal to a first mixer of the second primary receiver and route the signal to a second mixer of the second primary receiver.

A method for receiving a multiple carrier signal using a primary signal splitting carrier aggregation architecture and a 15 secondary signal splitting carrier aggregation architecture is also described. A first signal is received using a primary antenna. The first signal is routed through a first primary receiver on a transceiver chip in the primary signal splitting carrier aggregation architecture to obtain a first primary 20 inphase/quadrature signal. The first signal is routed through a first secondary receiver on the transceiver chip to obtain a first secondary inphase/quadrature signal. A second signal is received using a secondary antenna. The second signal is routed through a second primary receiver on a receiver chip in 25 the secondary signal splitting carrier aggregation architecture to obtain a second primary inphase/quadrature signal. The first signal is routed through a second secondary receiver on the receiver chip to obtain a second secondary inphase/ quadrature signal.

An apparatus for receiving a multiple carrier signal using a primary signal splitting carrier aggregation architecture and a secondary signal splitting carrier aggregation architecture is described. The apparatus includes means for receiving a first signal using a primary antenna. The apparatus also includes 35 means for routing the first signal through a first primary receiver on a transceiver chip in the primary signal splitting carrier aggregation architecture to obtain a first primary inphase/quadrature signal. The apparatus further includes means for routing the first signal through a first secondary 40 receiver on the transceiver chip to obtain a first secondary inphase/quadrature signal. The apparatus also includes means for receiving a second signal using a secondary antenna. The apparatus further includes means for routing the second signal through a second primary receiver on a receiver 45 chip in the secondary signal splitting carrier aggregation architecture to obtain a second primary inphase/quadrature signal. The apparatus also includes means for routing the first signal through a second secondary receiver on the receiver chip to obtain a second secondary inphase/quadrature signal. 50

# BRIEF DESCRIPTION OF THE DRAWINGS

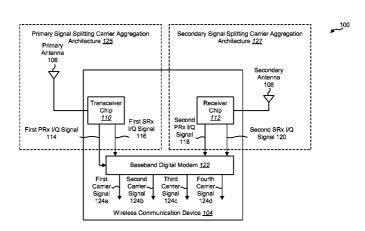

- FIG. 1 shows a wireless communication device for use in the present systems and methods;

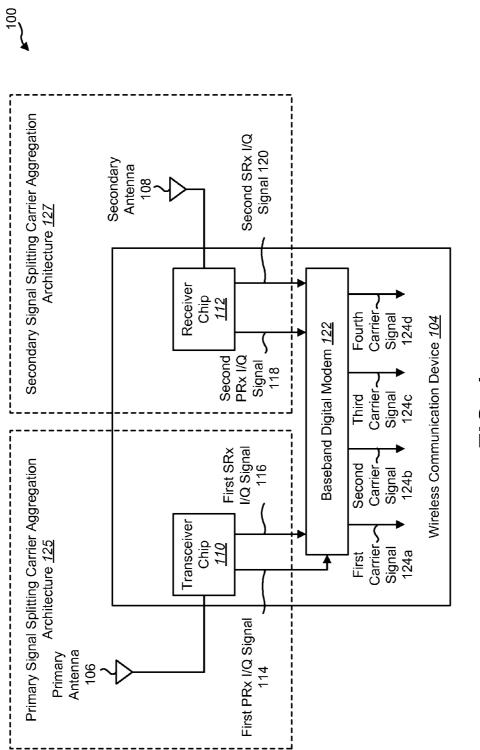

- FIG. 2 is a block diagram illustrating a primary signal splitting carrier aggregation architecture;

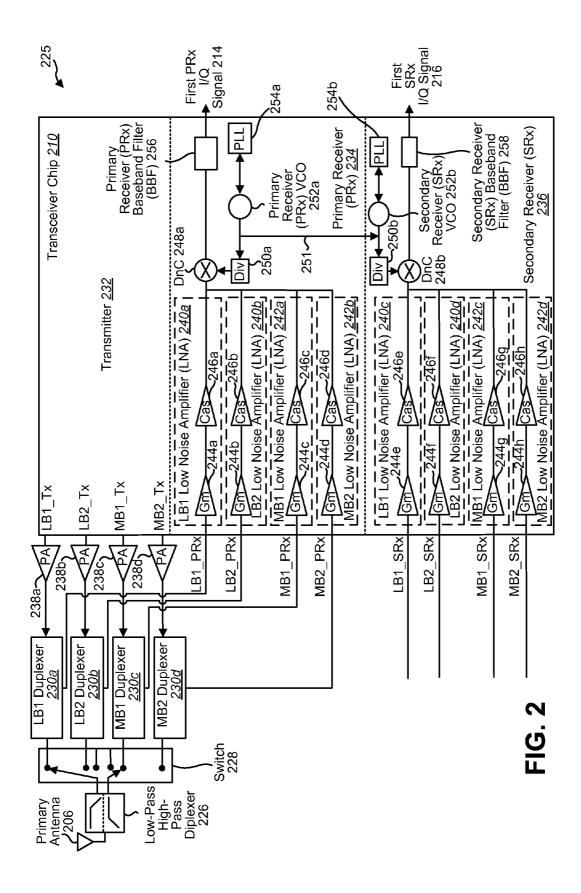

- FIG. 3 is a block diagram illustrating a secondary signal splitting carrier aggregation architecture;

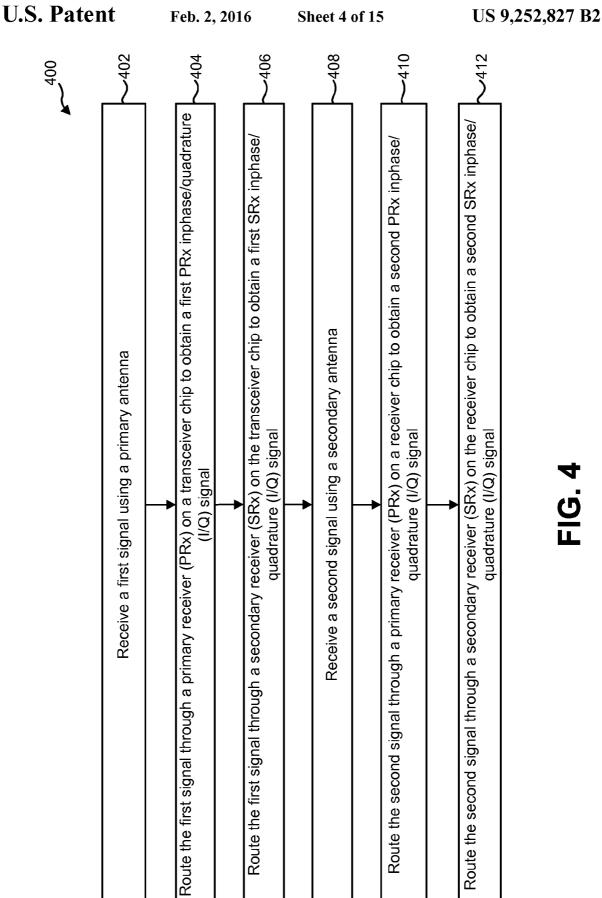

- FIG. **4** is a flow diagram of a method for receiving signals 60 using a signal splitting carrier aggregation architecture;

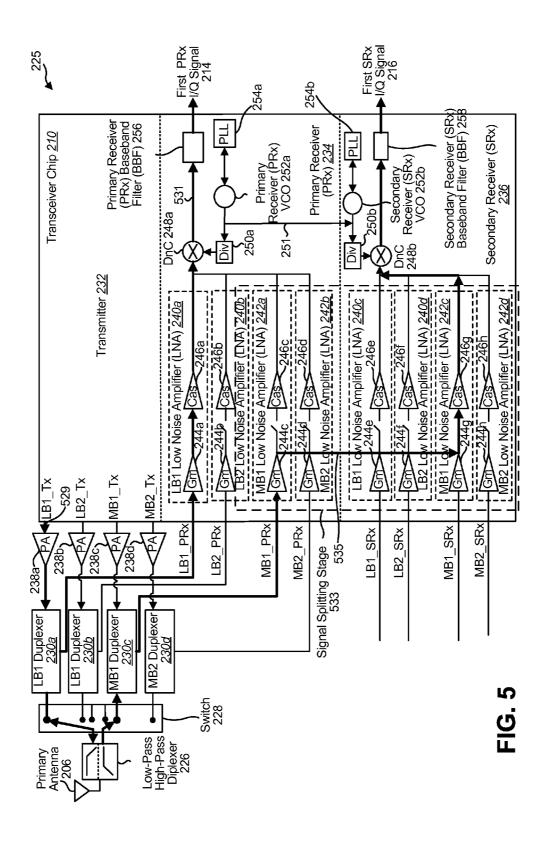

- FIG. 5 is a block diagram illustrating a primary signal splitting carrier aggregation architecture in inter-band operation:

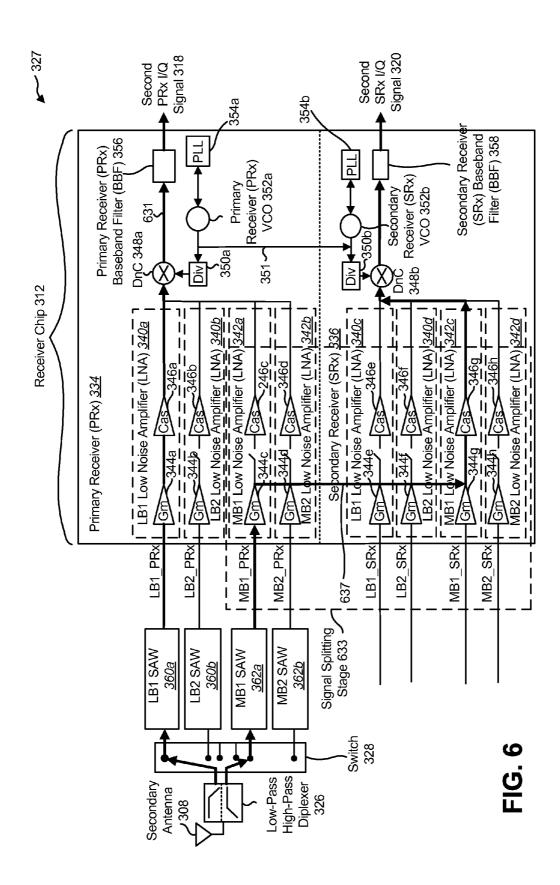

- FIG. **6** is a block diagram illustrating a secondary signal 65 splitting carrier aggregation architecture in inter-band operation:

4

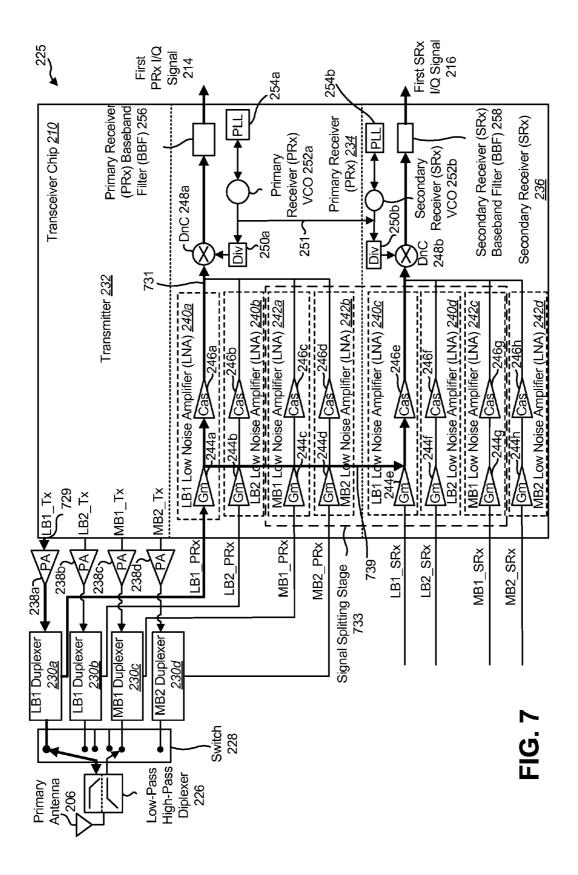

- FIG. 7 is a block diagram illustrating a primary signal splitting carrier aggregation architecture in intra-band operation:

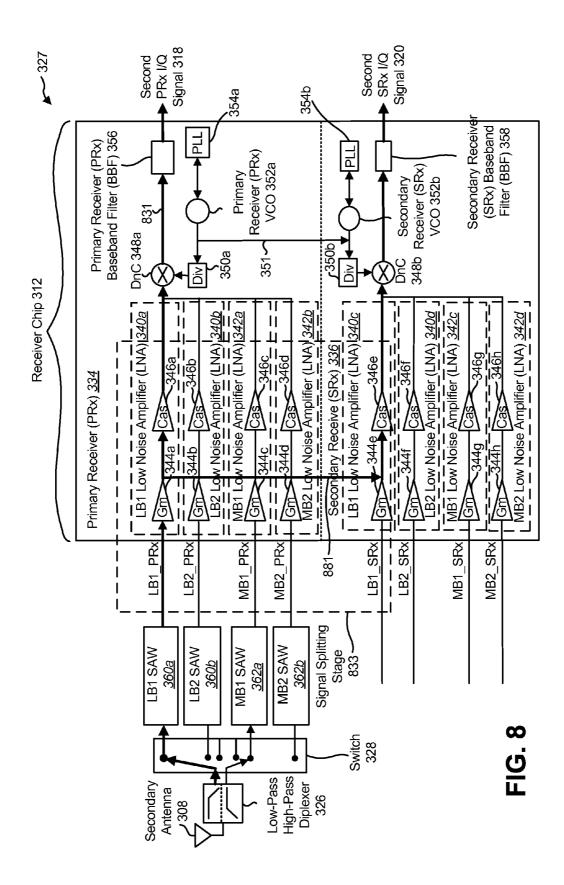

- FIG. 8 is a block diagram illustrating a secondary signal splitting carrier aggregation architecture in intra-band operation:

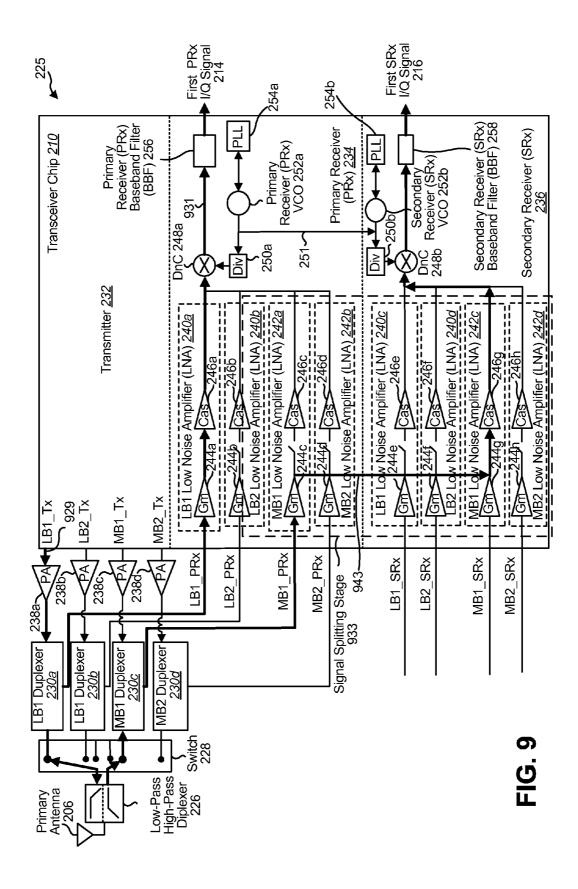

- FIG. 9 is a block diagram illustrating a primary signal splitting carrier aggregation architecture operating in interband simultaneous hybrid dual receiver (SHDR) mode;

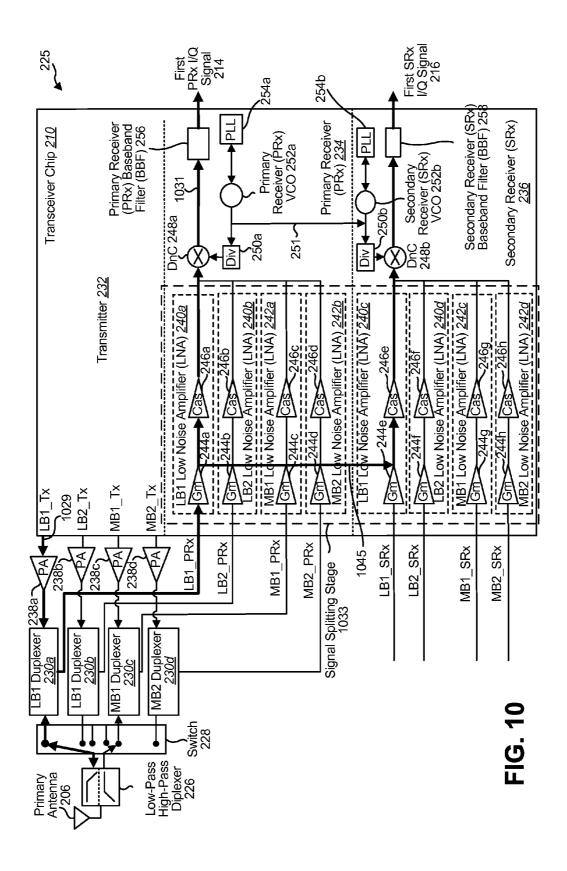

- FIG. 10 is a block diagram illustrating a primary signal splitting carrier aggregation architecture operating in intraband simultaneous hybrid dual receiver (SHDR) mode;

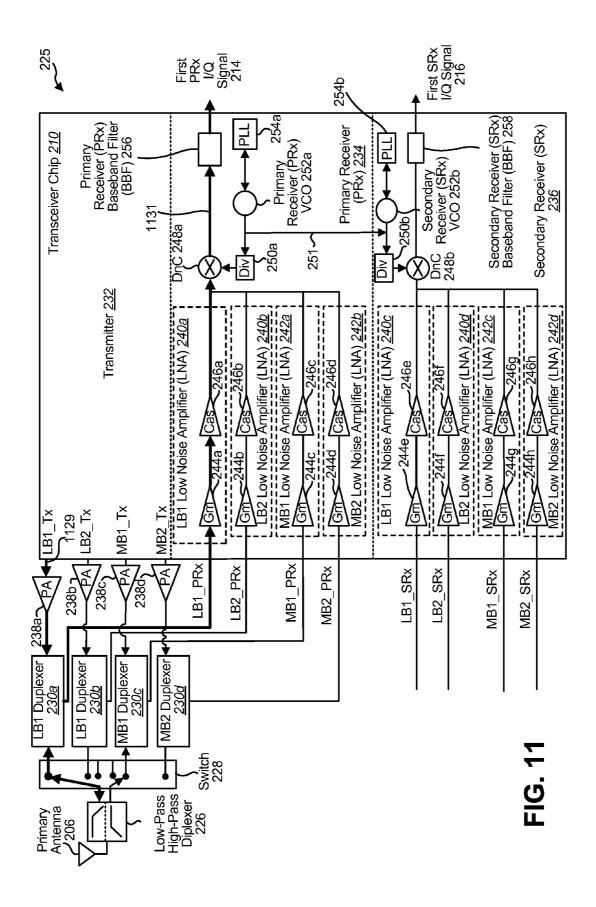

- FIG. 11 is a block diagram illustrating a primary signal splitting carrier aggregation architecture operating in diversity mode;

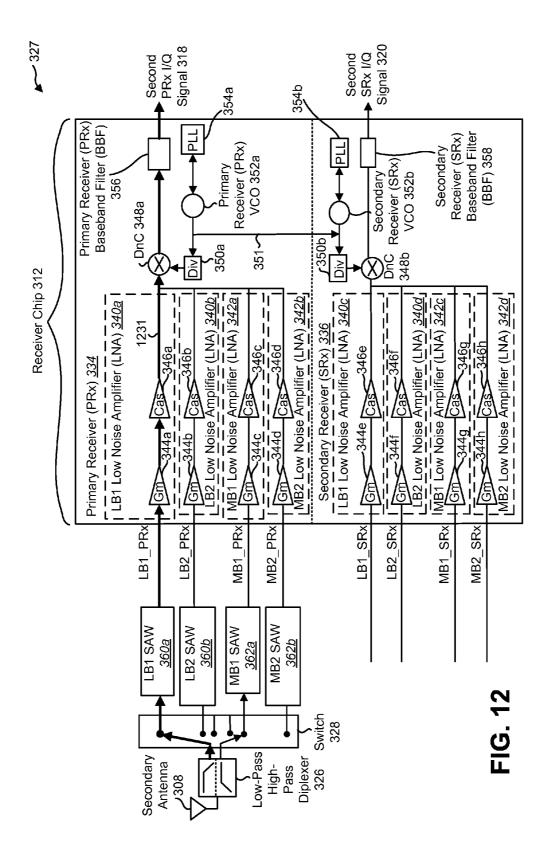

- FIG. 12 is a block diagram illustrating a secondary signal splitting carrier aggregation architecture operating in diversity mode;

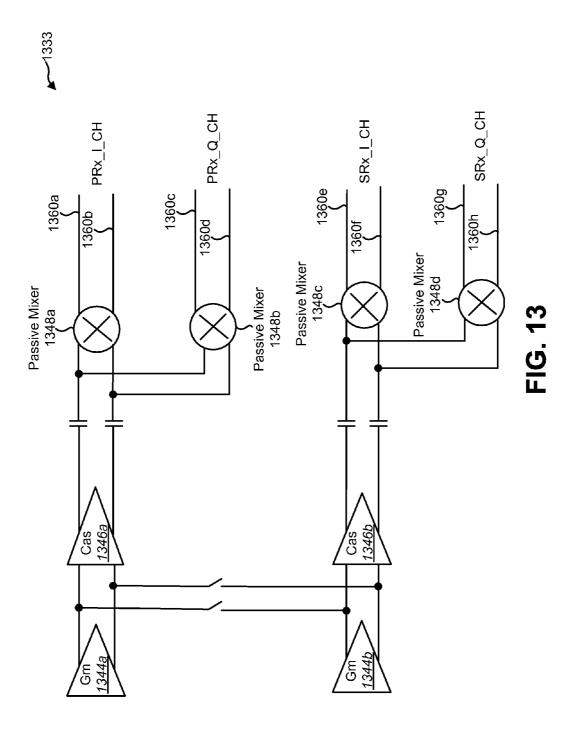

- FIG. 13 is a block diagram illustrating a signal splitting stage:

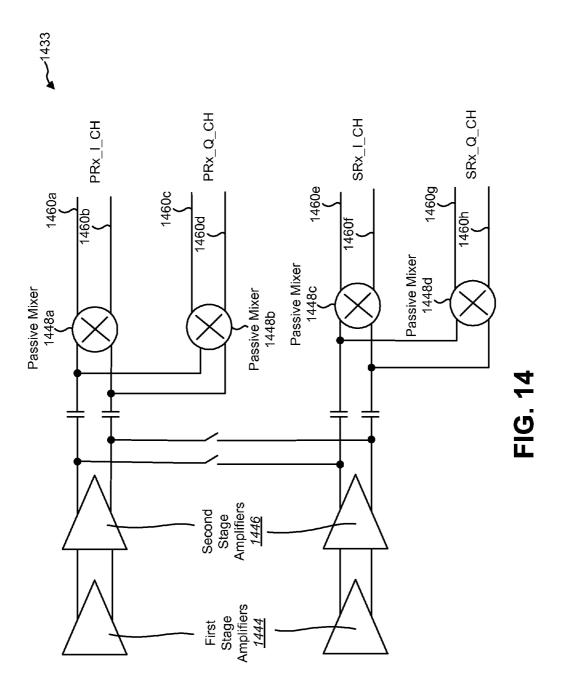

- FIG. 14 is a block diagram illustrating another signal splitting stage; and

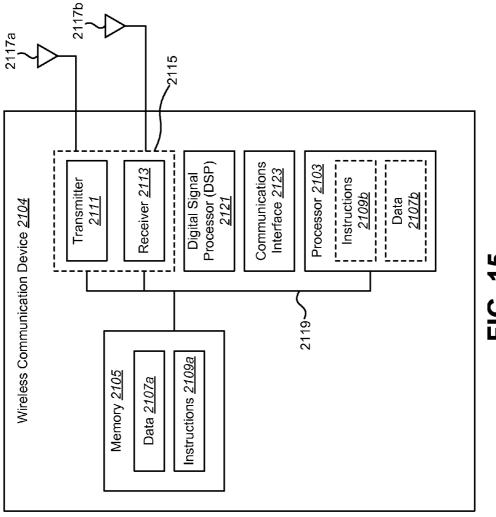

- FIG. 15 illustrates certain components that may be included within a wireless communication device.

### DETAILED DESCRIPTION

The 3<sup>rd</sup> Generation Partnership Project (3GPP) is a collaboration between groups of telecommunications associations that aims to define a globally applicable 3<sup>rd</sup> generation (3G) mobile phone specification. 3GPP Long Term Evolution (LTE) is a 3GPP project aimed at improving the Universal Mobile Telecommunications System (UMTS) mobile phone standard. The 3GPP may define specifications for the next generation of mobile networks, mobile systems and mobile devices. In 3GPP LTE, a mobile station or device may be referred to as a "user equipment" (UE).

3GPP specifications are based on evolved Global System for Mobile Communications (GSM) specifications, which are generally known as the Universal Mobile Telecommunications System (UMTS). 3GPP standards are structured as releases. Discussion of 3GPP thus frequently refers to the functionality in one release or another. For example, Release 99 specifies the first UMTS third generation (3G) networks, incorporating a CDMA air interface. Release 6 integrates operation with wireless local area networks (LAN) networks and adds High Speed Uplink Packet Access (HSUPA). Release 8 introduces dual downlink carriers and Release 9 extends dual carrier operation to uplink for UMTS.

CDMA2000 is a family of 3<sup>rd</sup> generation (3G) technology standards that use code division multiple access (CDMA) to send voice, data and signaling between wireless devices. CDMA2000 may include CDMA2000 1X, CDMA2000 EV-DO Rev. 0, CDMA2000 EV-DO Rev. A and CDMA2000 is EV-DO Rev. B. 1x or 1xRTT refers to the core CDMA2000 wireless air interface standard. 1x more specifically refers to 1 times Radio Transmission Technology and indicates the same radio frequency (RF) bandwidth as used in IS-95. 1xRTT adds 64 additional traffic channels to the forward link.

EV-DO refers to Evolution-Data Optimized. EV-DO is a telecommunications standard for the wireless transmission of data through radio signals.

FIG. 1 shows a wireless communication device 104 for use in the present systems and methods. A wireless communication device 104 may also be referred to as, and may include some or all of the functionality of, a terminal, an access terminal, a user equipment (UE), a subscriber unit, a station,

etc. A wireless communication device **104** may be a cellular phone, a personal digital assistant (PDA), a wireless device, a wireless modem, a handheld device, a laptop computer, a PC card, compact flash, an external or internal modem, a wireline phone, etc. A wireless communication device **104** may be 5 mobile or stationary. A wireless communication device **104** may communicate with zero, one or multiple base stations on a downlink and/or an uplink at any given moment. The downlink (or forward link) refers to the communication link from a base station to a wireless communication device **104**, and 10 the uplink (or reverse link) refers to the communication link from a wireless communication device **104** to a base station. Uplink and downlink may refer to the communication link or to the carriers used for the communication link.

A wireless communication device 104 may operate in a wireless communication system 100 that includes other wireless devices, such as base stations. A base station is a station that communicates with one or more wireless communication devices 104. A base station may also be referred to as, and may include some or all of the functionality of, an access 20 point, a broadcast transmitter, a Node B, an evolved Node B, etc. Each base station provides communication coverage for a particular geographic area. A base station may provide communication coverage for one or more wireless communication devices 104. The term "cell" can refer to a base station 25 and/or its coverage area, depending on the context in which the term is used.

Communications in a wireless communication system 100 (e.g., a multiple-access system) may be achieved through transmissions over a wireless link. Such a communication 30 link may be established via a single-input and single-output (SISO) or a multiple-input and multiple-output (MIMO) system. A multiple-input and multiple-output (MIMO) system includes transmitter(s) and receiver(s) equipped, respectively, with multiple (NT) transmit antennas and multiple 35 (NR) receive antennas for data transmission. SISO systems are particular instances of a multiple-input and multiple-output (MIMO) system. The multiple-input and multiple-output (MIMO) system can provide improved performance (e.g., higher throughput, greater capacity or improved reliability) if 40 the additional dimensionalities created by the multiple transmit and receive antennas are utilized.

The wireless communication system 100 may utilize both single-input and multiple-output (SIMO) and multiple-input and multiple-output (MIMO). The wireless communication 45 system 100 may be a multiple-access system capable of supporting communication with multiple wireless communication devices 104 by sharing the available system resources (e.g., bandwidth and transmit power). Examples of such multiple-access systems include code division multiple access 50 (CDMA) systems, wideband code division multiple access (W-CDMA) systems, time division multiple access (TDMA) systems, frequency division multiple access (FDMA) systems, orthogonal frequency division multiple access (OFDMA) systems, single-carrier frequency division mul- 55 tiple access (SC-FDMA) systems, 3<sup>rd</sup> Generation Partnership Project (3GPP) Long Term Evolution (LTE) systems and spatial division multiple access (SDMA) systems.

The wireless communication device 104 may utilize signal splitting. In signal splitting, signals are directed to a specific 60 path. One form of signal splitting is current steering. In one configuration of intra-band carrier aggregation, signal splitting refers to taking a signal from the output of a first stage amplifier (such as a transconductance stage (Gm)), splitting the signal and piping the signal into two separate primary and 65 secondary stage amplifiers (such as cascode stages (Cas)) and subsequent primary and diversity mixers for carrier aggrega-

6

tion. In another configuration of intra-band carrier aggregation, signal splitting refers to taking a signal from the output of a second stage amplifier (such as a cascode stage (Cas)), splitting the signal and piping the signal into two separate primary and diversity mixers for carrier aggregation.

In one configuration of inter-band carrier aggregation, signal splitting refers to taking a signal output from a first stage amplifier (such as a transconductance stage (Gm)) and steering (or diverting or pumping) the signal into a second stage amplifier (such as a cascode stage (Cas)) and subsequent mixer in the diversity path to be downconverted using a diversity local oscillator (LO). In another configuration of interband carrier aggregation, signal splitting refers to taking a signal output from a second stage amplifier (such as a cascode stage (Cas)) and steering (or diverting or pumping) the signal into a subsequent mixer in the diversity path to be downconverted using a diversity local oscillator (LO). The signal steering herein is current steering.

However, voltage steering may also be used. In one configuration of voltage steering for inter-band carrier aggregation, a signal output from a first stage amplifier (such as a transconductance stage (Gm)) may be diverted to a second stage amplifier (such as a cascode stage (Cas)) and subsequent mixer in the diversity path to be downconverted using a diversity local oscillator (LO). In another configuration of voltage steering for inter-band carrier aggregation, a signal output from a second stage amplifier (such as a cascode stage (Cas)) may be diverted to a subsequent mixer in the diversity path to be downconverted using a diversity local oscillator (LO).

The wireless communication device 104 may include a primary antenna 106 and a secondary antenna 108. The secondary antenna 108 may be referred to as the diversity antenna. A transceiver chip 110 may be coupled to the primary antenna 106. The transceiver chip 110 may include a transmitter, a primary receiver (PRx) and a secondary receiver (SRx). The transceiver chip 110 may output a first PRx inphase/quadrature (I/Q) signal 114 and a first SRx inphase/quadrature (I/Q) signal 116 to a baseband digital modem 122. The configuration of the primary antenna 106 and the transceiver chip 110 may be referred to as a primary signal splitting carrier aggregation architecture 125. The primary signal splitting carrier aggregation architecture 125 is discussed in additional detail below in relation to FIG. 2.

In general, the primary signal splitting carrier aggregation architecture 125 may split the received signal into the first PRx inphase/quadrature (I/Q) signal 114 using a low noise amplifier (LNA) in the primary receiver (PRx) and the first SRx inphase/quadrature (I/Q) signal 116 using a routing between a first low noise amplifier (LNA) in the primary receiver (PRx) and a second low noise amplifier (LNA) in the secondary receiver (SRx) of the transceiver chip 110. The routing may couple the output of a stage in the first low noise amplifier (LNA) to the input of a stage in the second low noise amplifier (LNA). There may be many different ways to split the signals. In one configuration, the stage in the first low noise amplifier (LNA) may be a transconductance stage (Gm) and the stage in the second low noise amplifier (LNA) may be a cascode stage (Cas). In another configuration, the first stage may be a transconductance stage (Gm) and the second stage may be a transformer used to split the signal.

A receiver chip 112 may be coupled to the secondary antenna 108. The receiver chip 112 may include both a primary receiver (PRx) and a secondary receiver (SRx). The receiver chip 112 may output a second PRx inphase/quadrature (I/Q) signal 118 and a second SRx inphase/quadrature (I/Q) signal 120 to the baseband digital modem 122. The

configuration of the secondary antenna 108 and the receiver chip 112 may be referred to as a secondary signal splitting carrier aggregation architecture 127. The secondary signal splitting carrier aggregation architecture 127 is discussed in additional detail below in relation to FIG. 3. In one configuration, the transceiver chip 110 may be located proximate to the primary antenna 106 on the wireless communication device 104 and the receiver chip 112 may be located proximate to the secondary antenna 108 on the wireless communication device 104. In other words, the transceiver chip 110 and the receiver chip 112 may not be proximate to each other.

In general, the secondary signal splitting carrier aggregation architecture 127 may split the received signal into the second PRx inphase/quadrature (I/Q) signal 118 using a low noise amplifier (LNA) in the primary receiver (PRx) and the 15 second SRx inphase/quadrature (I/Q) signal 120 using a routing between a first low noise amplifier (LNA) in the primary receiver (PRx) and a second low noise amplifier (LNA) in the secondary receiver (SRx) of the receiver chip 112. There may be many different ways to split the signals. In one configuration, the stage in the first low noise amplifier (LNA) may be a transconductance stage (Gm) and the stage in the second low noise amplifier (LNA) may be a cascode stage (Cas). In another configuration, the first stage may be a transconductance stage (Gm) and the second stage may be a transformer 25 used to split the signal.

The wireless communication device 104 may use a signal splitting carrier aggregation architecture that reuses the diversity/simultaneous hybrid dual receiver (SHDR) path. Carrier aggregation may be achieved by coupling the primary 30 receiver (PRx) signal in a chip (i.e., in the transceiver chip 110 and the receiver chip 112) to the diversity receiver (DRx) path. One advantage of the signal splitting carrier aggregation architecture of the present systems and methods is the ability to operate using only two antennas. Because a wireless communication device 104 with less antennas is cheaper, less bulky and less complicated, a wireless communication device 104 with the minimum number of antennas may be advantageous

The wireless communication device 104 of the present 40 systems and methods does not require the use of a power splitter. By removing a power splitter from the wireless communication device 104, the wireless communication device 104 may consume less power. Furthermore, the lack of a power splitter may reduce the cost of the wireless communi- 45 cation device 104 and free up die area. The signal splitting carrier aggregation architecture of the present systems and methods may also not require the use of external low noise amplifiers (LNAs). External low noise amplifiers (LNAs) may consume large amounts of power and increase the cost of 50 a wireless communication device 104. Another benefit of the signal splitting carrier aggregation architecture of the present systems and methods is the ability to operate without die-todie signal routing. Removing die-to-die signal routing may reduce both the complexity and cost of the wireless commu- 55 nication device 104. Removing die-to-die signaling may also allow for optimal placement of antennas on the wireless communication device 104. The signal splitting carrier aggregation architecture may have four synthesizers running.

The baseband digital modem 122 may perform processing 60 on the first PRx inphase/quadrature (I/Q) signal 114, the second PRx inphase/quadrature (I/Q) signal 118, the first SRx inphase/quadrature (I/Q) signal 116 and the second SRx inphase/quadrature (I/Q) signal 120. For example, the baseband digital modem 122 may convert the signals to the digital 65 domain using analog-to-digital converters (ADCs) and perform digital processing on the signals using digital signal

8

processors (DSPs). The baseband digital modem 122 may then output a first carrier signal 124a, a second carrier signal 124b, a third carrier signal 124c and a fourth carrier signal 124d. A carrier signal may refer to the carrier that the signal used.

In one configuration, the first carrier signal 124a and the second carrier signal 124b may be located in the low band while the third carrier signal 124c and the fourth carrier signal 124d are located within the midband. This may be referred to as inter-band operation or Dual-Band 4-Carrier according to Rel-10. Inter-band operation is discussed in additional detail below in relation to FIG. 5 and FIG. 6 below. In another configuration, the first carrier signal 124a, second carrier signal 124b, third carrier signal 124c and fourth carrier signal 124d may all be located within a single band, such as the low band. This may be referred to as intra-band operation or Single-Band 4-Carrier in Release-10. Intra-band operation is discussed in additional detail below in relation to FIG. 7 and FIG. 8 below.

In another configuration, the wireless communication device 104 may operate in simultaneous hybrid dual receiver (SHDR) mode. In simultaneous hybrid dual receiver (SHDR) mode, only the transceiver chip 110 may be used (i.e., the receiver chip 112 may be disabled). The configuration of the transceiver chip 110 operating in inter-band simultaneous hybrid dual receiver (SHDR) mode is discussed below in relation to FIG. 9. The configuration of the transceiver chip 110 operating in intra-band simultaneous hybrid dual receiver (SHDR) mode is discussed below in relation to FIG. 10.

In yet another configuration, the wireless communication device 104 may operate in diversity mode. In diversity mode, both the transceiver chip 110 and the receiver chip 112 are tuned to receive the same carrier frequency. The configuration of the transceiver chip 110 operating in diversity mode is discussed below in relation to FIG. 11. The configuration of the receiver chip 112 operating in diversity mode is discussed below in relation to FIG. 12.

FIG. 2 is a block diagram illustrating a primary signal splitting carrier aggregation architecture 225. The primary signal splitting carrier aggregation architecture 225 of FIG. 2 may be one configuration of the primary signal splitting carrier aggregation architecture 125 of FIG. 1. The primary signal splitting carrier aggregation architecture 125 may include a primary antenna 206, a low-pass high-pass diplexer 226, a switch 228, four duplexers 230a-d and a transceiver chip 210. The primary antenna 206 may be coupled to the low-pass high-pass diplexer 226. The low-pass high-pass diplexer 226 may bundle low band frequencies into one signal and high band (or midband) frequencies into another signal, thus allowing the primary antenna 206 to pass both low band and midband signals to the transceiver chip 210.

The low-pass high-pass diplexer 226 may be coupled to the switch 228. The switch 228 may have two inputs (the signal that includes the bundled low band frequencies and the signal that includes the bundled high band frequencies) and multiple outputs. In one configuration, the switch 228 may have six possible outputs to the four duplexers 230 (representing the six possible configurations of duplexer 230 pairs). The four duplexers 230 may include a first low band (LB1) duplexer 230a, a second low band (LB2) duplexer 230b, a first midband (MB1) duplexer 230c and a second midband (MB2) duplexer 230d.

As discussed above, the transceiver chip 210 may include a transmitter 232, a primary receiver (PRx) 234 and a secondary receiver (SRx) 236. The transmitter 232 may include two low band outputs (LB1\_Tx and LB2\_Tx) and two midband outputs (MB1\_Tx and MB2\_Tx). The first low band output

(LB1\_Tx) may be coupled to the first low band (LB1) duplexer 230a via a power amplifier (PA) 238a. The second low band output (LB2\_Tx) may be coupled to the second low band (LB2) duplexer 230b via a power amplifier 238b. The first midband output (MB1\_Tx) may be coupled to the first midband (MB1) duplexer 230c via a power amplifier 238c. The second midband output (MB2\_Tx) may be coupled to the second midband (MB2) duplexer 230d via a power amplifier 238d.

The primary receiver (PRx) 234 may include a first low 10 band input (LB1 PRx) coupled to the first low band (LB1) duplexer 230a, a second low band input (LB2\_PRx) coupled to the second low band (LB2) duplexer 230b, a first midband input (MB1\_PRx) coupled to the first midband (MB1) duplexer 230c and a second midband input (MB2 PRx) coupled to the second midband (MB2) duplexer 230d. The first low band input (LB1\_PRx) may be coupled to a first low band (LB1) low noise amplifier (LNA) 240a that includes a transconductance stage (Gm) 244a and a cascode stage (Cas) **246***a*. The second low band input (LB2 PRx) may be coupled 20 to a second low band (LB2) low noise amplifier (LNA) 240b that includes a transconductance stage (Gm) 244b and a cascode stage (Cas)  $\bf 246\it b$ . The first midband input (MB1\_PRx) may be coupled to a first midband (MB1) low noise amplifier (LNA) **242***a* that includes a transconductance stage (Gm) 25 **244**c and a cascode stage (Cas) **246**c. The second midband input (MB2\_PRx) may be coupled to a second midband (MB2) low noise amplifier (LNA) 242a that includes a transconductance stage (Gm) 244d and a cascode stage (Cas)

The primary receiver (PRx) **234** may also include a down-converter (DnC) **248***a*. The downconverter (DnC) **248***a* may be coupled to the output of the first low band (LB1) low noise amplifier (LNA) **240***a*, the output of the second low band (LB2) low noise amplifier (LNA) **240***b*, the output of the first 35 midband (MB1) low noise amplifier (LNA) **242***a* and the output of the second midband (MB2) low noise amplifier (LNA) **242***b*.

The primary receiver (PRx) **234** may include a phase locked loop (PLL) **254***a*, a voltage controlled oscillator 40 (VCO) **252***a* and a Div stage **250***a* that are used to generate the downconverting frequency for the downconverter (DnC) **248***a*. The output of the downconverter (DnC) **248***a* may be coupled to a primary receiver (PRx) baseband filter (BBF) **256**. The primary receiver (PRx) baseband filter (BBF) **256** may then output the first PRx inphase/quadrature (I/Q) signal **214**.

The secondary receiver (SRx) 236 may include a first low band input (LB1\_SRx), a second low band input (LB2\_SRx), a first midband input (MB1\_SRx) and a second midband 50 input (MB2 SRx) that are disabled. The first low band input (LB1 SRx) may be coupled to a first low band (LB1) low noise amplifier (LNA) 240c that includes a transconductance stage (Gm) **244***e* and a cascode stage (Cas) **246***e*. The second low band input (LB2\_SRx) may be coupled to a second low 55 band (LB2) low noise amplifier (LNA) 240d that includes a transconductance stage (Gm) 244f and a cascode stage (Cas) **246**f. The first midband input (MB1\_SRx) may be coupled to a first midband (MB1) low noise amplifier (LNA) 242c that includes a transconductance stage (Gm) 244g and a cascode 60 stage (Cas) 246g. The second midband input (MB2 SRx) may be coupled to a second midband (MB2) low noise amplifier (LNA) **242**d that includes a transconductance stage (Gm) **244**h and a cascode stage (Cas) **246**h. In one configuration, the first low band (LB1) low noise amplifier (LNA) 240c, the second low band (LB2) low noise amplifier (LNA) 240d, the first midband (MB1) low noise amplifier (LNA) 242c and the

10

second midband (MB2) low noise amplifier (LNA) 242d of the secondary receiver (SRx) 236 may each be disabled. However, portions within some of the low noise amplifiers (LNAs) 240c-d, 242c-d may still be used (e.g., the transconductance stage (Gm) 244 and the Cascode stage (Cas) 246) to allow the reuse of the diversity/simultaneous hybrid dual receiver (SHDR) receiver path (i.e., for the primary signal splitting carrier aggregation architecture 225).

The secondary receiver (SRx) 236 may also include a downconverter (DnC) 248b. The downconverter (DnC) 248b may be coupled to the output of the first low band (LB1) low noise amplifier (LNA) 240c, the output of the second low band (LB2) low noise amplifier (LNA) 240d, the output of the first midband (MB1) low noise amplifier (LNA) 242c and the output of the second midband (MB2) low noise amplifier (LNA) 242d. The secondary receiver (SRx) 236 may further include a phase locked loop (PLL) 254b, a voltage controlled oscillator (VCO) 252b and a Div stage 250b that are used to generate the downconverting frequency for the downconverter (DnC) 248b.

The output of the downconverter (DnC) **248***b* may be coupled to a secondary receiver (SRx) baseband filter (BBF) **258**. The secondary receiver (SRx) baseband filter (BBF) **258** may then output the first SRx inphase/quadrature (I/Q) signal **216**. In one configuration, the secondary receiver (SRx) **236** may not include the secondary receiver (SRx) voltage controlled oscillator (VCO) **252***b* and the phase locked loop (PLL) **254***b* or the secondary receiver (SRx) voltage controlled oscillator (VCO) **252***b* and the phase locked loop (PLL) **254***b* may be disabled. Instead, the transceiver chip **210** may pump the same voltage controlled oscillator (VCO) signal **251** used in the primary receiver (PRx) **234** to the secondary receiver (SRx) **236**.

FIG. 3 is a block diagram illustrating a secondary signal splitting carrier aggregation architecture 327. The secondary signal splitting carrier aggregation architecture 327 of FIG. 3 may be one configuration of the secondary signal splitting carrier aggregation architecture 127 of FIG. 1. The secondary signal splitting carrier aggregation architecture 327 may include a secondary antenna 308, a low-pass high-pass diplexer 326, a switch 328, four surface acoustic wave (SAW) filters 360a-b, 362a-b and a receiver chip 312. The secondary antenna 308 may be coupled to the low-pass high-pass diplexer 326. The low-pass high-pass diplexer 326 may bundle low band frequencies into one signal and high band (or mid band) frequencies into another signal, thus allowing the secondary antenna 308 to pass both low band and mid band signals to the receiver chip 312.

The low-pass high-pass diplexer 326 may be coupled to the switch 328. The switch 328 may have two inputs (the signal that includes the bundled low band frequencies and the signal that includes the bundled high band frequencies) and multiple outputs. In one configuration, the switch 328 may have six possible outputs to the four surface acoustic wave (SAW) filters 360, 362 (representing the four possible configurations of surface acoustic wave (SAW) filter 360, 362 pairs). The four surface acoustic wave (SAW) filters 360, 362 may include a first low band (LB1) surface acoustic wave (SAW) filter 360a, a second low band (LB2) surface acoustic wave (SAW) filter 360b, a first midband (MB1) surface acoustic wave (SAW) filter 362a and a second midband (MB2) surface acoustic wave (SAW) filter 362b.

The receiver chip 312 may include a primary receiver (PRx) 334 and a secondary receiver (SRx) 336. The primary receiver (PRx) 334 may include a first low band input (LB1\_PRx) coupled to the first low band (LB1) surface acoustic wave (SAW) filter 360a, a second low band input

(LB2\_PRx) coupled to the second low band (LB2) surface acoustic wave (SAW) filter 360b, a first midband input (MB1\_PRx) coupled to the first midband (MB1) surface acoustic wave (SAW) filter 362a and a second midband input (MB2\_PRx) coupled to the second midband (MB2) surface 5 acoustic wave (SAW) filter 362b. The first low band input (LB1\_PRx) may be coupled to a first low band (LB1) low noise amplifier (LNA) 340a that includes a transconductance stage (Gm) 344a and a cascode stage (Cas) 346a. The second low band input (LB2\_PRx) may be coupled to a second low band (LB2) low noise amplifier (LNA) 340b that includes a transconductance stage (Gm) 344b and a cascode stage (Cas) **346***b*. The first midband input (MB1\_PRx) may be coupled to a first midband (MB1) low noise amplifier (LNA) 342a that includes a transconductance stage (Gm) 344c and a cascode 15 stage (Cas) 346c. The second midband input (MB2\_PRx) may be coupled to a second midband (MB2) low noise amplifier (LNA) 342b that includes a transconductance stage (Gm) **344***d* and a cascode stage (Cas) **346***d*.

The primary receiver (PRx) **334** may also include a down-converter (DnC) **348***a*. The downconverter (DnC) **348***a* may be coupled to the output of the first low band (LB1) low noise amplifier (LNA) **340***a*, the output of the second low band (LB2) low noise amplifier (LNA) **340***b*, the output of the first midband (MB1) low noise amplifier (LNA) **342***a* and the 25 output of the second midband (MB2) low noise amplifier (LNA) **342***b*.

The primary receiver (PRx) **334** may include a phase locked loop (PLL) **354***a*, a voltage controlled oscillator (VCO) **352***a* and a Div stage **350***a* that are used to generate the downconverting frequency for the downconverter (DnC) **348***a*. The output of the downconverter (DnC) **348***a* may be coupled to a primary receiver (PRx) baseband filter (BBF) **356**. The primary receiver (PRx) baseband filter (BBF) **356** may then output the second PRx inphase/quadrature (I/Q) 35 signal **318**.

The secondary receiver (SRx) 336 may include a first low band input (LB1 SRx), a second low band input (LB2 SRx), a first midband input (MB1\_SRx) and a second midband input (MB2\_SRx) that are disabled. The first low band input 40 (LB1\_SRx) may be coupled to a first low band (LB1) low noise amplifier (LNA) 340c that includes a transconductance stage (Gm) 344e and a cascode stage (Cas) 346e. The second low band input (LB2\_SRx) may be coupled to a second low band (LB2) low noise amplifier (LNA) 340d that includes a 45 transconductance stage (Gm) 344f and a cascode stage (Cas) **346**f. The first midband input (MB1 SRx) may be coupled to a first midband (MB1) low noise amplifier (LNA) 342c that includes a transconductance stage (Gm) 344g and a cascode stage (Cas) 346g. The second midband input (MB2\_SRx) 50 may be coupled to a second midband (MB2) low noise amplifier (LNA) 342d that includes a transconductance stage (Gm) **344**h and a cascode stage (Cas) **346**h. In one configuration, the first low band (LB1) low noise amplifier (LNA) 340c, the second low band (LB2) low noise amplifier (LNA) 340d, the 55 first midband (MB1) low noise amplifier (LNA) 342c and the second midband (MB2) low noise amplifier (LNA) 342d may each be disabled. However, portions within some of the low noise amplifiers (LNAs) 340c-d, 342c-d may still be used (e.g., the transconductance stage (Gm) 344 and the cascode 60 stage (Cas) 346) to allow the reuse of the diversity/simultaneous hybrid dual receiver (SHDR) receiver path (i.e., for the secondary signal splitting carrier aggregation architecture 327).

The secondary receiver (SRx) **336** may also include a 65 downconverter (DnC) **348**b. The downconverter (DnC) **348**b may be coupled to the output of the first low band (LB1) low

12

noise amplifier (LNA) 340c, the output of the second low band (LB2) low noise amplifier (LNA) 340d, the output of the first midband (MB1) low noise amplifier (LNA) 342c and the output of the second midband (MB2) low noise amplifier (LNA) 342d. The secondary receiver (SRx) 336 may further include a phase locked loop (PLL) 354b, a voltage controlled oscillator (VCO) 352b and a Div stage 350b that are used to generate the downconverting frequency for the downconverter (DnC) 348b. The output of the downconverter (DnC) 348b may be coupled to a secondary receiver (SRx) baseband filter (BBF) 358. The secondary receiver (SRx) baseband filter (BBF) 358 may then output the second SRx inphase/ quadrature (I/Q) signal 320. In one configuration, the secondary receiver (SRx) 336 may not include the secondary receiver (SRx) voltage controlled oscillator (VCO) 352b and the phase locked loop (PLL) 354b or the secondary receiver (SRx) voltage controlled oscillator (VCO) 352b and the phase locked loop (PLL) 354b may be disabled. Instead, the receiver chip 312 may pump the same voltage controlled oscillator (VCO) signal 351 used in the primary receiver (PRx) 334 to the secondary receiver (SRx) 336.

FIG. 4 is a flow diagram of a method 400 for receiving signals using a signal splitting carrier aggregation architecture. The method 400 may be performed by a wireless communication device 104. The wireless communication device 104 may receive 402 a first signal using a primary antenna 106. The wireless communication device 104 may route 404 the first signal through a primary receiver (PRx) 234 on a transceiver chip 110 to obtain a first PRx inphase/quadrature (I/Q) signal 114. The wireless communication device 104 may also route 406 the first signal through a secondary receiver (SRx) 236 on the transceiver chip 110 to obtain a first SRx inphase/quadrature (I/Q) signal 116.